# **CprE 281: Digital Logic**

**Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

### **Fast Adders**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

### **Administrative Stuff**

- No HW is due next Monday

- HW 6 will is due on Monday Oct. 14 @ 10 pm.

#### **Administrative Stuff**

- Labs next week

- Mini-Project

- This is worth 3% of your grade (x2 labs)

- https://www.ece.iastate.edu/~alexs/classes/ 2024\_Fall\_2810/labs/Project-Mini/

# Three Different Ways to Represent Negative Integer Numbers

- Sign and magnitude

- 1's complement

- 2's complement

# Three Different Ways to Represent Negative Integer Numbers

- Sign and magnitude

- 1's complement

- 2's complement

only this method is used in modern computers

## Interpretation of four-bit signed integers

| $b_3b_2b_1b_0$ | Sign and<br>magnitude | 1's complement | 2's complement |

|----------------|-----------------------|----------------|----------------|

| 0111           | +7                    | +7             | +7             |

| 0110           | +6                    | +6             | +6             |

| 0101           | +5                    | +5             | +5             |

| 0100           | +4                    | +4             | +4             |

| 0011           | +3                    | +3             | +3             |

| 0010           | +2                    | +2             | +2             |

| 0001           | +1                    | +1             | +1             |

| 0000           | +0                    | +0             | +0             |

| 1000           | -0                    | -7             | -8             |

| 1001           | -1                    | -6             | -7             |

| 1010           | -2                    | -5             | -6             |

| 1011           | -3                    | -4             | -5             |

| 1100           | -4                    | -3             | -4             |

| 1101           | -5                    | -2             | -3             |

| 1110           | -6                    | -1             | -2             |

| 1111           | -7                    | -0             | -1             |

### Interpretation of four-bit signed integers

| $b_3b_2b_1b_0$ | Sign and<br>magnitude | 1's complement | 2's complement |

|----------------|-----------------------|----------------|----------------|

| 0111           | +7                    | +7             | +7             |

| 0110           | +6                    | +6             | +6             |

| 0101           | +5                    | +5             | +5             |

| 0100           | +4                    | +4             | +4             |

| 0011           | +3                    | +3             | +3             |

| 0010           | +2                    | +2             | +2             |

| 0001           | +1                    | +1             | +1             |

| 0000           | +0                    | +0             | +0             |

| 1000           | -0                    | -7             | -8             |

| 1001           | -1                    | -6             | -7             |

| 1010           | -2                    | -5             | -6             |

| 1011           | -3                    | -4             | -5             |

| 1100           | -4                    | -3             | -4             |

| 1101           | -5                    | -2             | -3             |

| 1110           | -6                    | -1             | -2             |

| 1111           | -7                    | -0             | -1             |

Note that each table includes both positive and negative integers.

[ Table 3.2 from the textbook ]

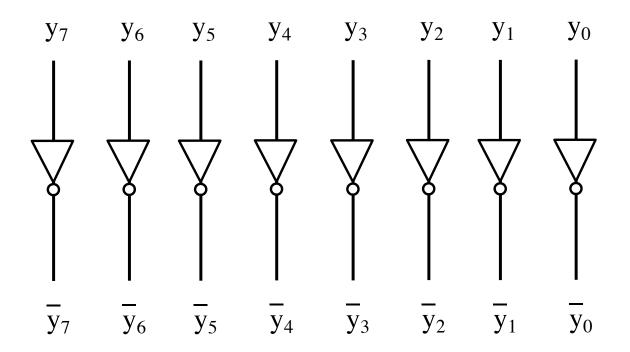

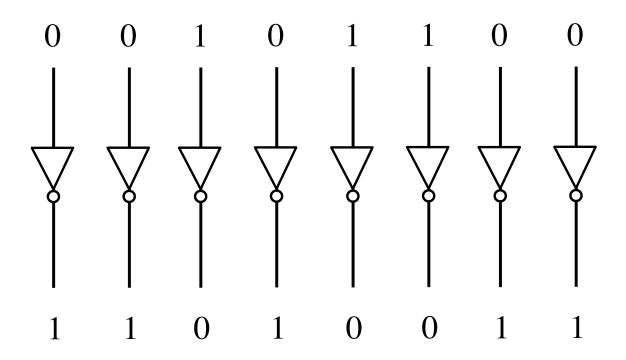

## 1's Complement

1's complement (subtract each digit from 1)

| _ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

|---|---|---|---|---|---|---|---|---|--|

|   | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |  |

|   | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |  |

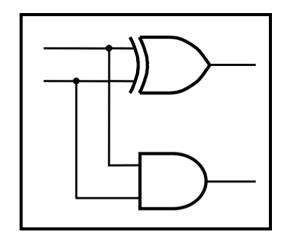

# Circuit for negating a number stored in 1's complement representation

# Circuit for negating a number stored in 1's complement representation

## 2's Complement

## 2's complement representation (4-bit)

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

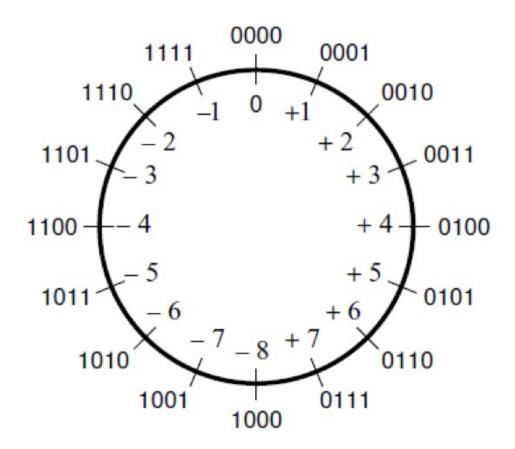

### The number circle for 2's complement

0 1 0 1

1110

1 1 0 0

0 1 1 1

0 1 0 1 1 0 1 0 1 1 1 0

0001

1 1 0 0 0 0 1 1  $0\ 1\ 1\ 1$   $1\ 0\ 0\ 0$

Invert all bits...

$$\begin{array}{r}

1 \ 1 \ 1 \ 0 \\

+ \ 0 \ 0 \ 1 \\

\hline

0 \ 0 \ 1 \ 0

\end{array}$$

$$\begin{array}{r}

1100 \\

+0011 \\

\hline

0100

\end{array}$$

$$\begin{array}{r}

0 \ 1 \ 1 \ 1 \\

+ \ 1 \\

\hline

1 \ 0 \ 0 \ 1

\end{array}$$

.. then add 1.

# Circuit #1 for negating a number stored in 2's complement representation

# Circuit #2 for negating a number stored in 2's complement representation

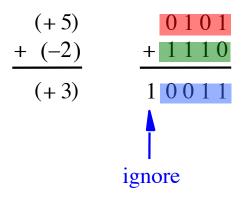

# Addition of two numbers stored in 2's complement representation

•

$$(+5)$$

+  $(-2)$

•

$$(-5)$$

+  $(-2)$

```

• (+5) + (+2) positive plus positive

```

•

$$(-5)$$

+  $(-2)$  negative plus negative

## Positive plus positive

$$(+5)$$

$+(+2)$

$(+7)$

$0101$

$+0010$

$0111$

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

| 1111           | -1             |

## **Negative plus positive**

$$\begin{array}{ccc}

(-5) & & 1011 \\

+ (+2) & & + 0010 \\

\hline

& & & & & \\

\hline

& & & & & \\

& & & & & \\

\end{array}$$

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

### Positive plus negative

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

## **Negative plus negative**

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

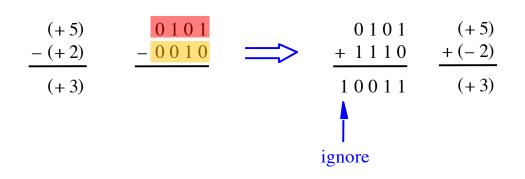

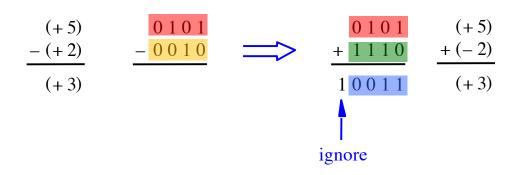

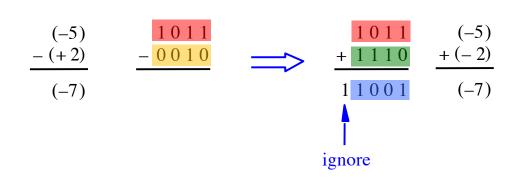

# Subtraction of two numbers stored in 2's complement representation

```

• (+5) - (+2) positive minus positive

```

•

$$(-5)$$

-  $(-2)$  negative minus negative

•

$$(-5)$$

-  $(-2)$

•

$$(+5)$$

-  $(+2)$  =  $(+5)$  +  $(-2)$

•  $(-5)$  -  $(+2)$  =  $(-5)$  +  $(-2)$

•  $(+5)$  -  $(-2)$  =  $(+5)$  +  $(+2)$

•  $(-5)$  -  $(-2)$  =  $(-5)$  +  $(+2)$

•

$$(+5)$$

-  $(+2)$  =  $(+5)$  +  $(-2)$

•  $(-5)$  -  $(+2)$  =  $(-5)$  +  $(-2)$

•  $(+5)$  -  $(-2)$  =  $(+5)$  +  $(+2)$

•  $(-5)$  -  $(-2)$  =  $(-5)$  +  $(+2)$

We can change subtraction into addition ...

•

$$(+5)$$

-  $(+2)$  =  $(+5)$  +  $(-2)$

•  $(-5)$  -  $(+2)$  =  $(-5)$  +  $(-2)$

•  $(+5)$  -  $(-2)$  =  $(+5)$  +  $(+2)$

•  $(-5)$  -  $(-2)$  =  $(-5)$  +  $(+2)$

... if we negate the second number.

•

$$(+5)$$

-  $(+2)$  =  $(+5)$  +  $(-2)$

•  $(-5)$  -  $(+2)$  =  $(-5)$  +  $(-2)$

•  $(+5)$  -  $(-2)$  =  $(+5)$  +  $(+2)$

$$\bullet \ (-5) - (-2) = (-5) + (+2)$$

These are the four addition cases (arranged in a shuffled order)

## **Start with: Positive minus positive**

$$\begin{array}{c}

(+5) \\

-(+2) \\

\hline

(+3)

\end{array}$$

$$\begin{array}{c}

0 \ 1 \ 0 \ 1 \\

-0 \ 0 \ 1 \ 0 \\

\end{array}$$

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

#### Convert to: Positive plus negative

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                |                |

#### Convert to: Positive plus negative

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                |                |

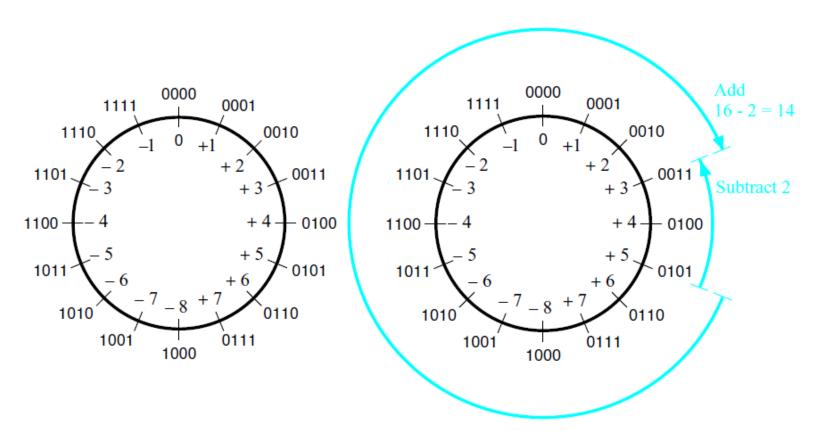

# Graphical interpretation of four-bit 2's complement numbers

(a) The number circle

(b) Subtracting 2 by adding its 2's complement

#### **Start with: Negative minus positive**

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| -3-2-1-0       | T              |

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                | _              |

#### Convert to: Negative plus negative

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

#### **Start with: Positive minus negative**

$$\begin{array}{ccc}

(+5) & & 0101 \\

- & (-2) & & -1110 \\

\hline

& (+7) & & \end{array}$$

| 02             |

|----------------|

| 2's complement |

| +7             |

| +6             |

| +5             |

| +4             |

| +3             |

| +2             |

| +1             |

| +0             |

| -8             |

| -7             |

| -6             |

| -5             |

| -4             |

| -3             |

| -2             |

| -1             |

|                |

#### Convert to: Positive plus positive

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                |                |

#### **Start with: Negative minus negative**

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                |                |

#### Convert to: Negative plus positive

| $b_3b_2b_1b_0$ | 2's complement |

|----------------|----------------|

| 0111           | +7             |

| 0110           | +6             |

| 0101           | +5             |

| 0100           | +4             |

| 0011           | +3             |

| 0010           | +2             |

| 0001           | +1             |

| 0000           | +0             |

| 1000           | -8             |

| 1001           | -7             |

| 1010           | -6             |

| 1011           | -5             |

| 1100           | -4             |

| 1101           | -3             |

| 1110           | -2             |

| 1111           | -1             |

|                |                |

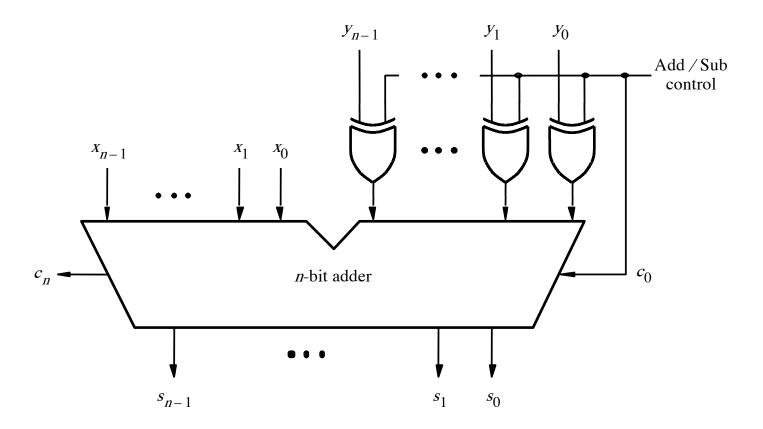

#### **Take Home Message**

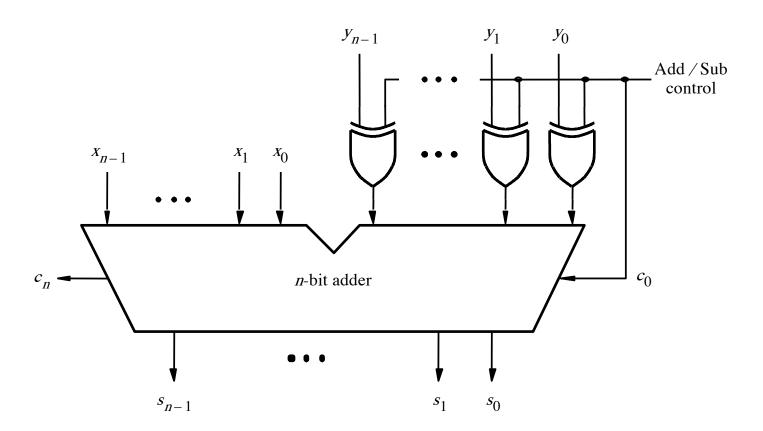

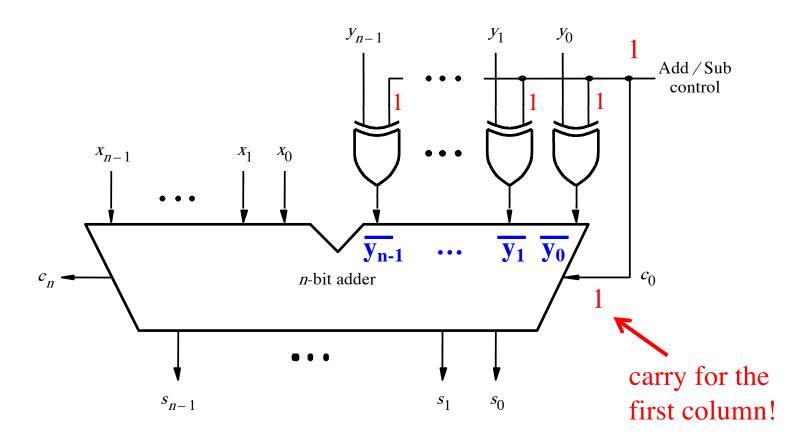

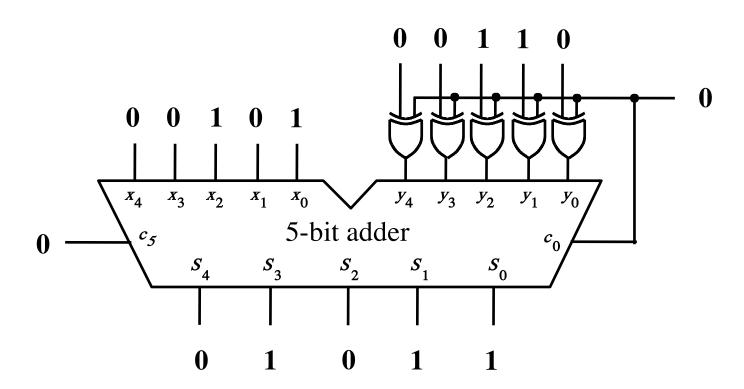

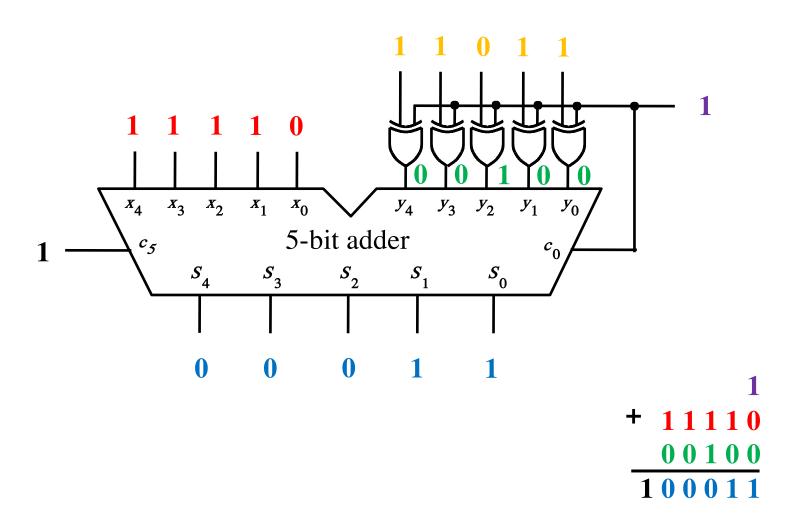

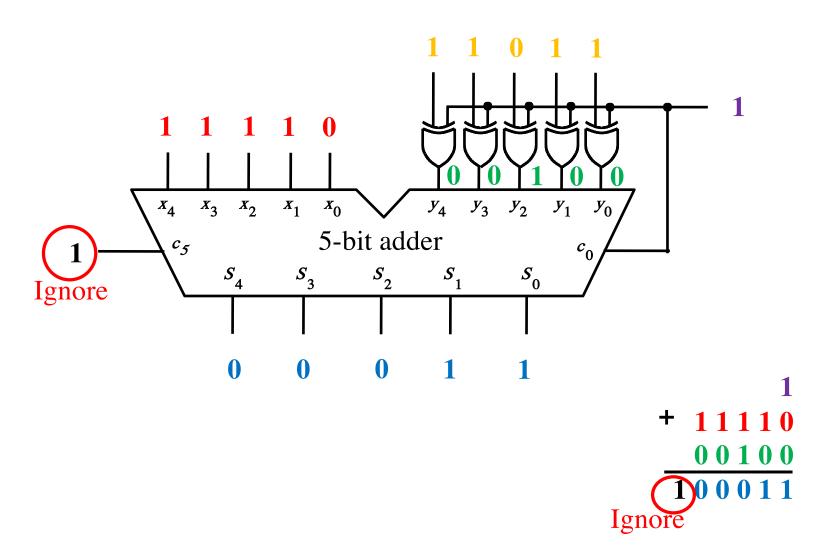

Subtraction can be performed by simply negating the second number and adding it to the first, regardless of the signs of the two numbers.

Thus, the same adder circuit can be used to perform both addition and subtraction !!!

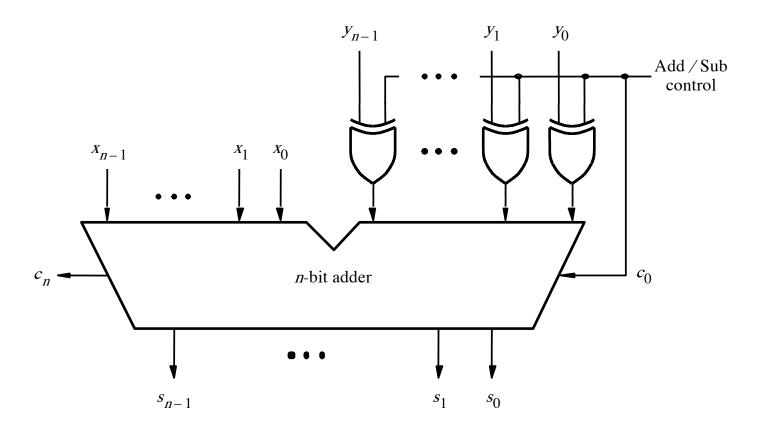

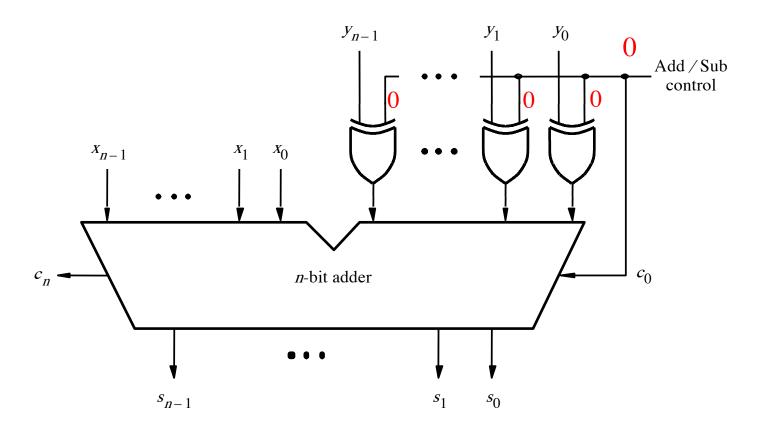

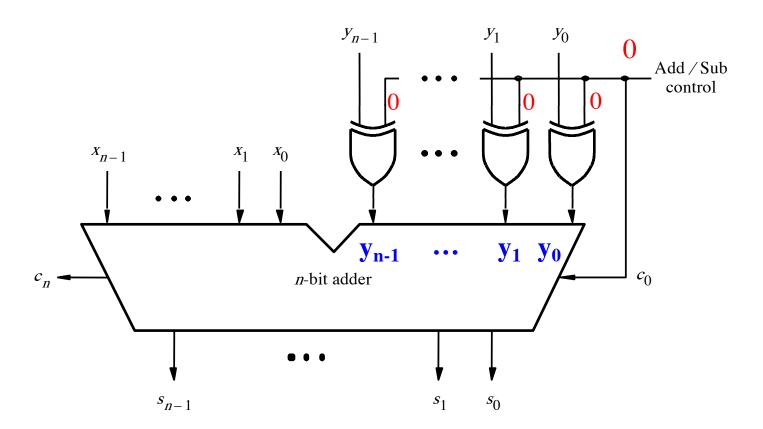

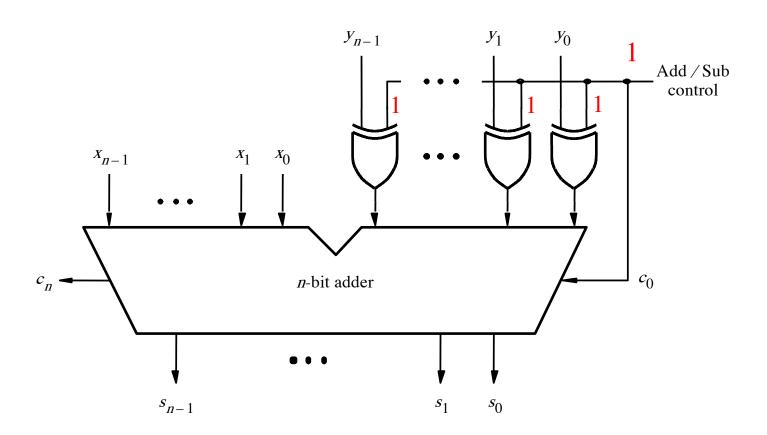

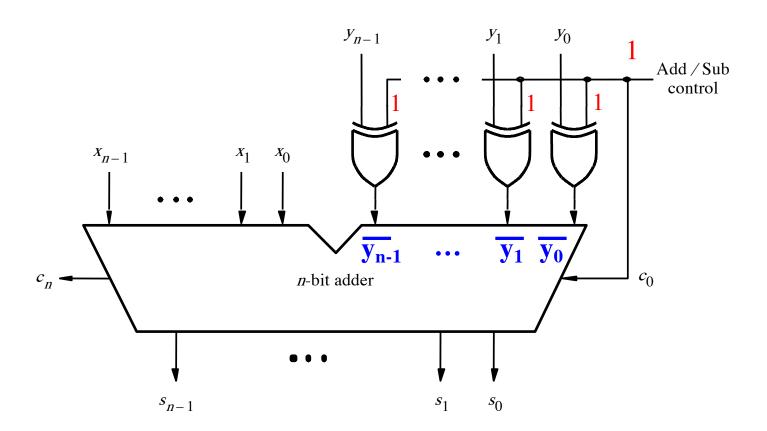

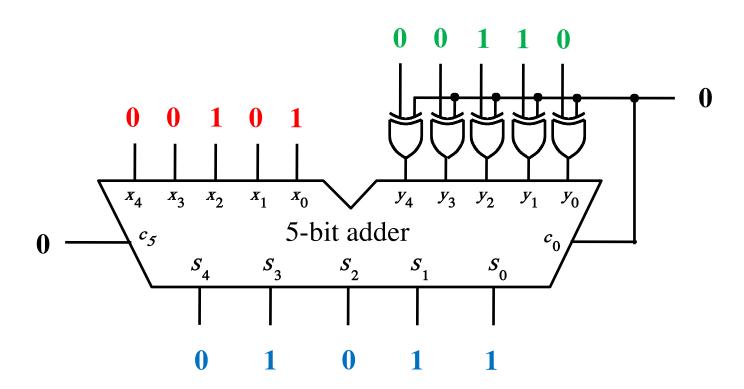

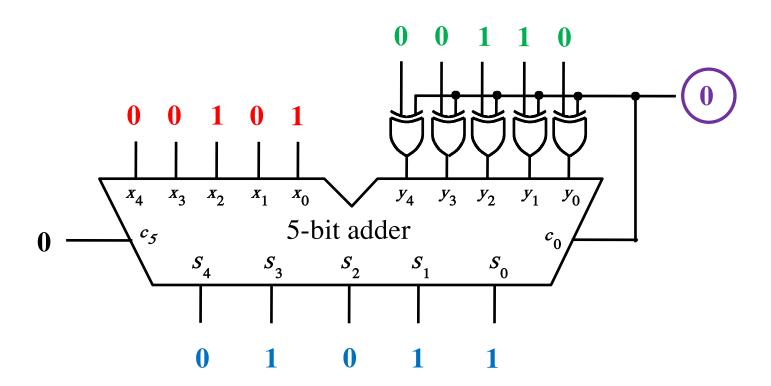

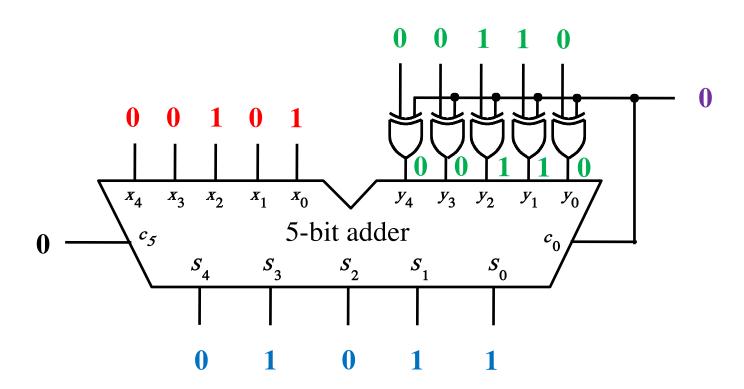

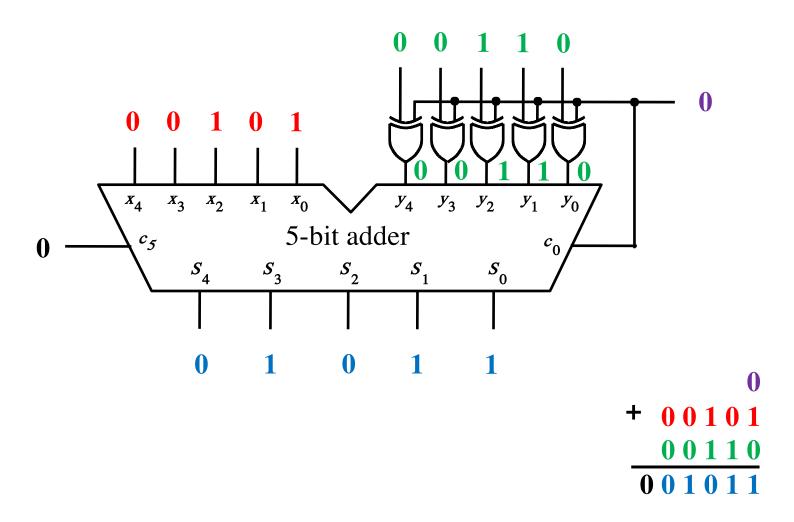

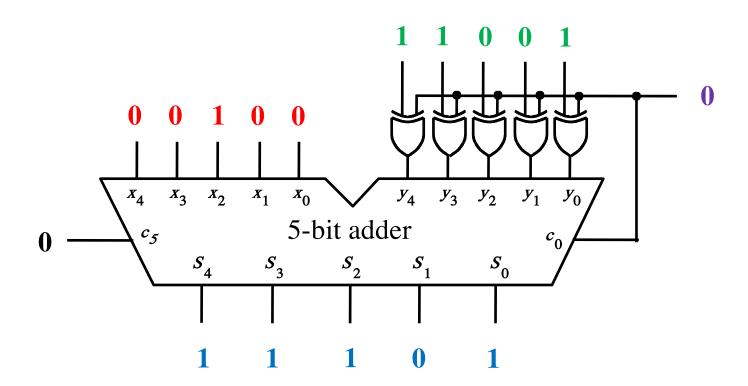

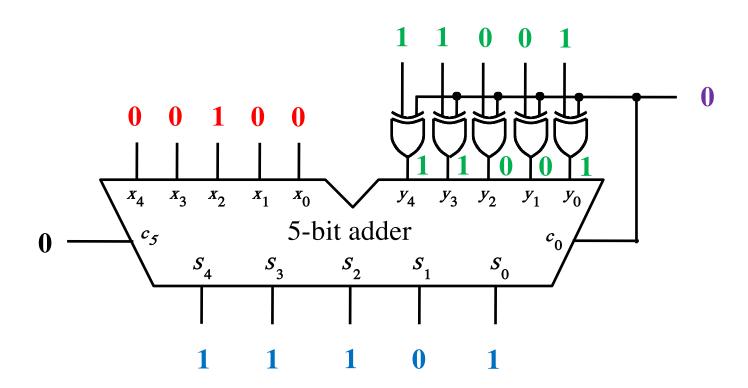

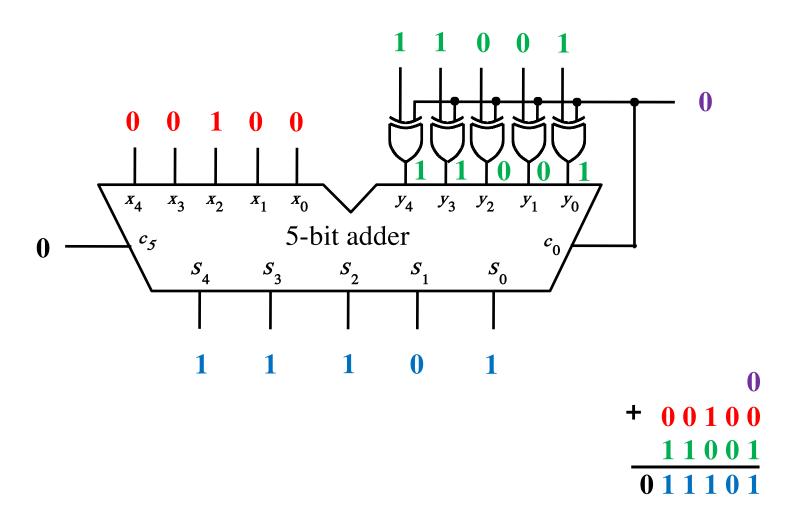

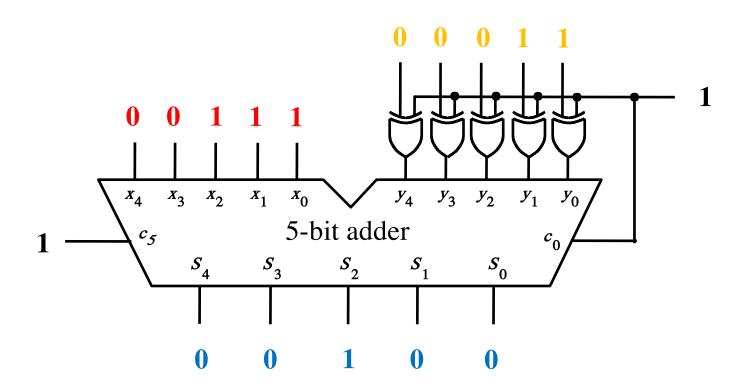

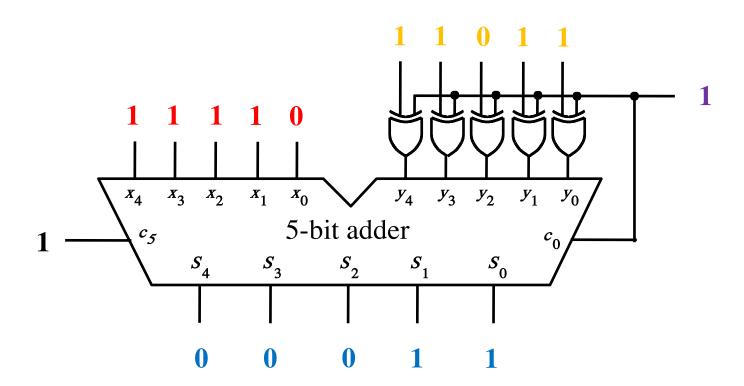

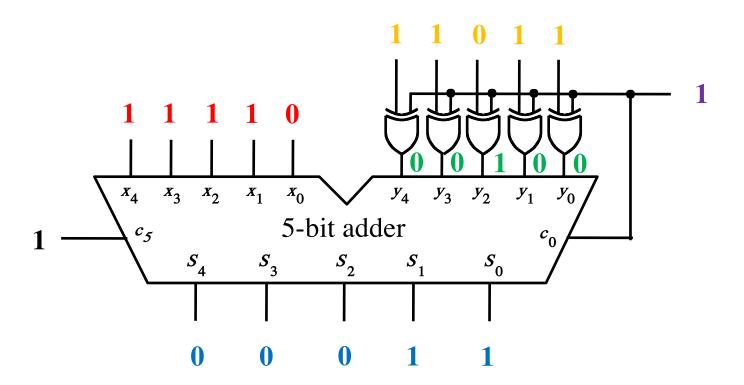

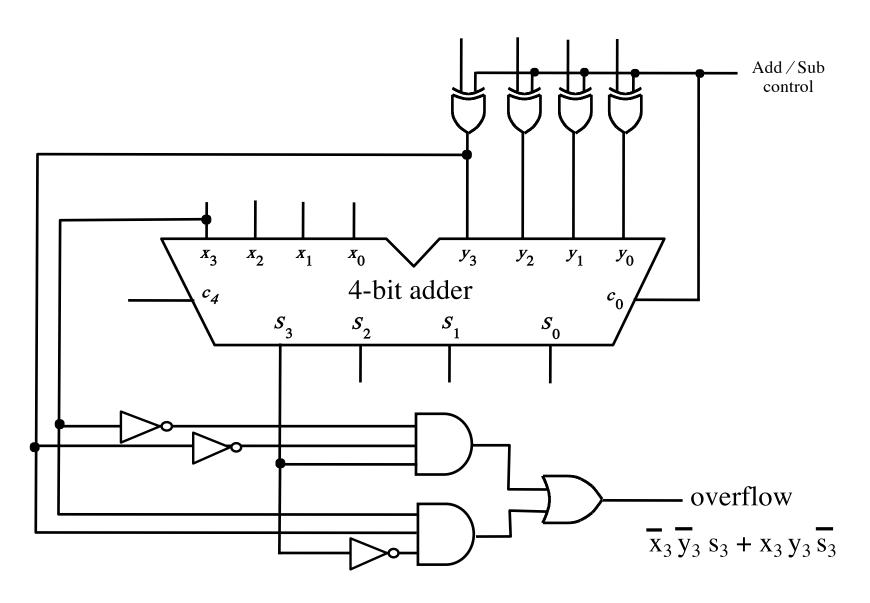

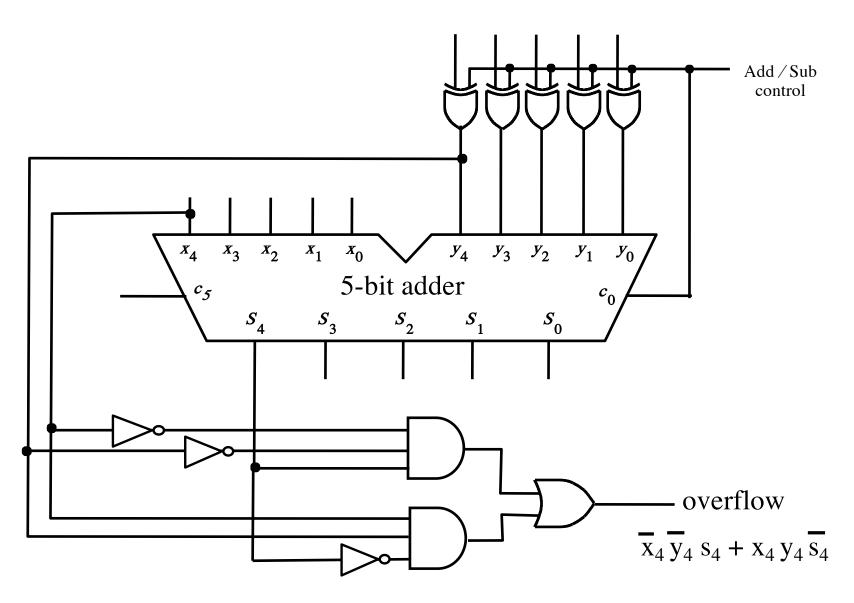

#### Adder/subtractor unit

[ Figure 3.12 from the textbook ]

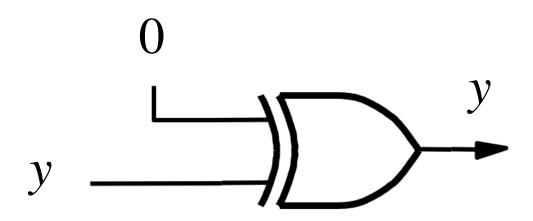

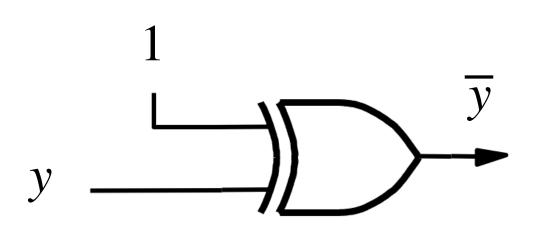

#### **XOR Tricks**

| control | y | out |

|---------|---|-----|

| 0       | 0 | 0   |

| 0       | 1 | 1   |

| 1       | 0 | 1   |

| 1       | 1 | 0   |

|         |   |     |

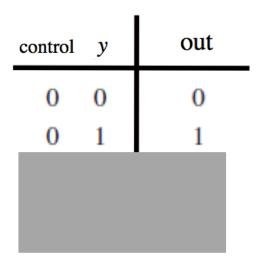

# XOR as a repeater

## XOR as a repeater

| control | у | out |

|---------|---|-----|

| 0       | 0 | 0   |

| 0       | 1 | 1   |

|         |   |     |

|         |   |     |

|         |   |     |

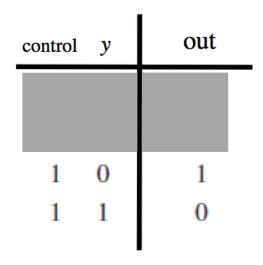

#### XOR as an inverter

#### XOR as an inverter

| control y | out |  |

|-----------|-----|--|

|           |     |  |

| 1 0       | 1   |  |

| 1 1       | 0   |  |

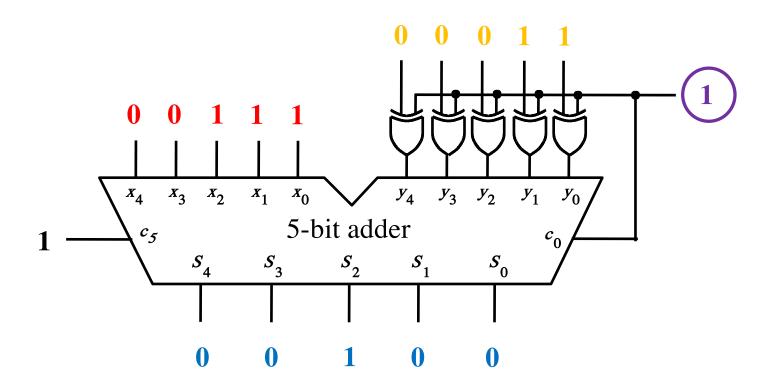

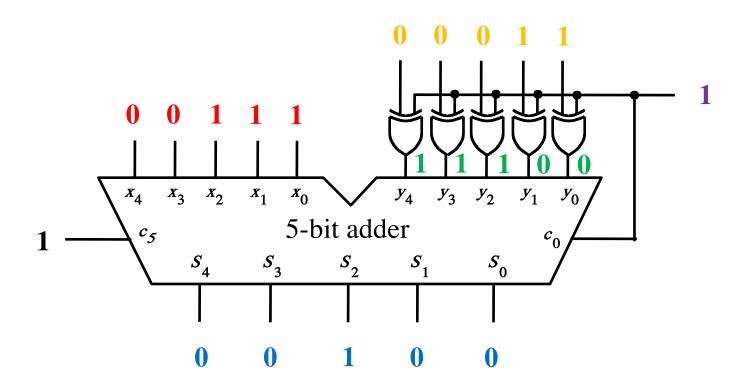

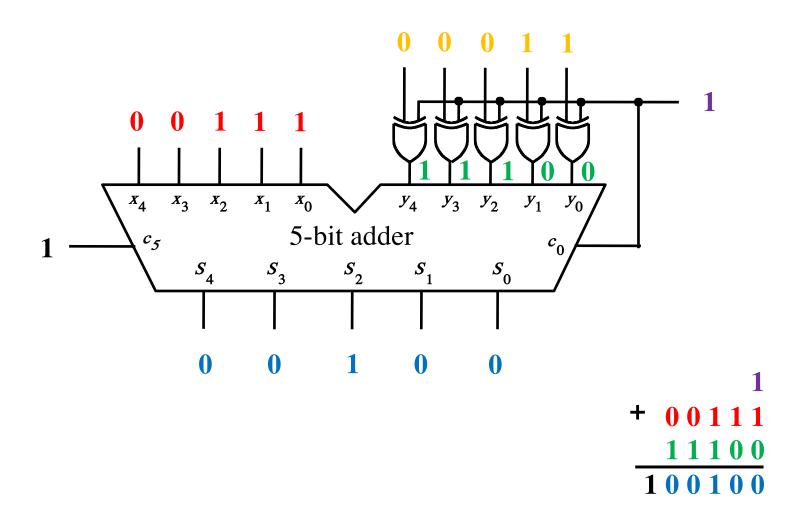

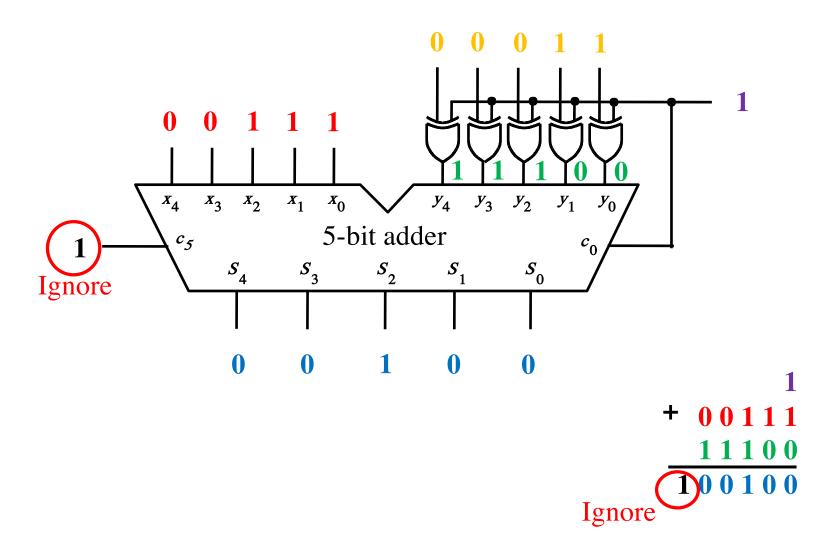

#### Addition: when control = 0

[ Figure 3.12 from the textbook ]

#### Addition: when control = 0

[ Figure 3.12 from the textbook ]

#### Addition: when control = 0

[ Figure 3.12 from the textbook ]

[ Figure 3.12 from the textbook ]

[ Figure 3.12 from the textbook ]

[ Figure 3.12 from the textbook ]

[ Figure 3.12 from the textbook ]

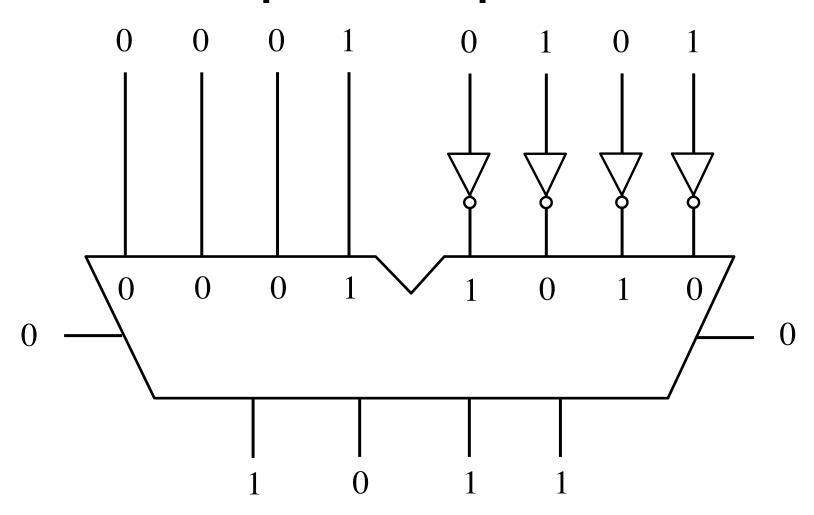

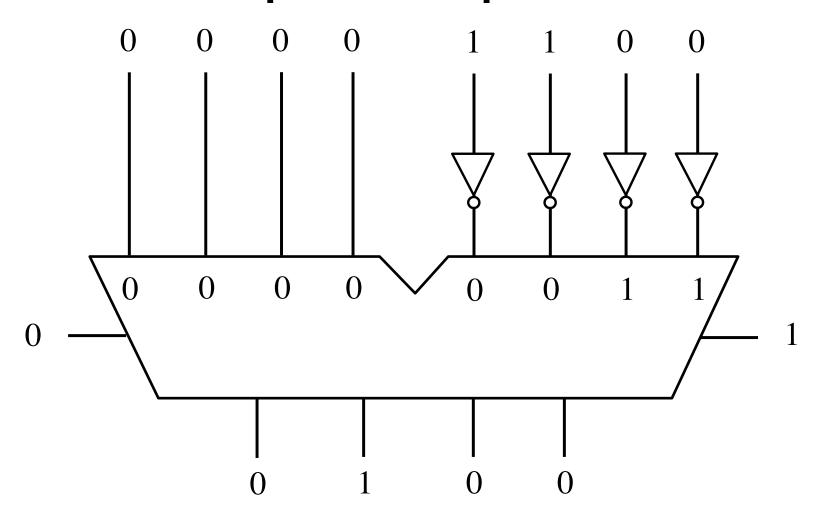

# Addition Examples: all inputs and outputs are given in 2's complement representation

## Addition: 4 + (-7) = -3

## Addition: 4 + (-7) = -3

# Addition: 4 + (-7) = -3

# Subtraction Examples: all inputs and outputs are given in 2's complement representation

### **Analogy: Another Way to Do Subtraction**

9's complement = 82 + (35 + 1)10's complement = 82 + 36 - 100// Add the first two. 118 - 100 // Just delete the leading 1. // No need to subtract 100. 18

#### **Overflow Detection**

$$\frac{(-7)}{+(+2)} + \frac{1001}{0010}$$

$$\frac{(-5)}{1011}$$

$$\frac{(-7)}{+(-2)} + \frac{1001}{1110}$$

$$\frac{(-9)}{10111}$$

$$\begin{array}{c}

(+7) \\

+(+2) \\

\hline

(+9)

\end{array}

+

\begin{array}{c}

0 \ 1 \ 1 \ 1 \\

0 \ 0 \ 1 \ 0 \\

\hline

1 \ 0 \ 0 \ 1

\end{array}$$

$$\frac{(-7)}{+(+2)} + \frac{1001}{0010}$$

$$\frac{(-5)}{1011}$$

$$\begin{array}{ccc}

(+7) & + & 0111 \\

+ & 1110 \\

\hline

(+5) & 10101

\end{array}$$

In 2's complement, both +9 and -9 are not representable with 4 bits.

$$\begin{array}{c}

(+7) \\

+(+2) \\

\hline

(+9)

\end{array}

+

\begin{array}{c}

0 1 1 0 0 \\

0 1 1 1 \\

0 0 1 0 \\

\hline

1 0 0 1

\end{array}$$

$$\begin{array}{c}

(+7) \\

+ (-2) \\

\hline

(+5)

\end{array}

+ \begin{array}{c}

11100 \\

0111 \\

1110 \\

\hline

10101

\end{array}$$

Include the carry bits:  $c_4 c_3 c_2 c_1 c_0$

$$\begin{array}{c}

(+7) \\

+(+2) \\

(+9)

\end{array}

+

\begin{array}{c}

0 \ 1 \ 1 \ 0 \ 0 \\

0 \ 1 \ 1 \ 1 \\

0 \ 0 \ 1 \ 0 \\

1 \ 0 \ 0 \ 1

\end{array}$$

$$\begin{array}{c}

(+7) \\

+ (-2) \\

\hline

(+5)

\end{array}

+ \begin{array}{c}

11100 \\

0111 \\

1110 \\

\hline

10101$$

Include the carry bits:  $c_4 c_3 c_2 c_1 c_0$

$$c_{4} = 0$$

$$c_{3} = 1$$

$$(+7)$$

$$+ (+2)$$

$$(+9)$$

$$0 1 1 0 0$$

$$0 1 1 1$$

$$0 0 1 0$$

$c_4 = 0$ <br/> $c_3 = 0$

Include the carry bits:

$$c_4 c_3 c_2 c_1 c_0$$

$$\begin{array}{c}

c_4 = 0 \\

c_3 = 1

\end{array} + \begin{array}{c}

(+7) \\

+ (+2)

\end{array} + \begin{array}{c}

0 \ 1 \ 1 \ 0 \ 0 \ 1 \ 1 \\

0 \ 0 \ 1 \ 0 \\

\hline

1 \ 0 \ 0 \ 1

\end{array}$$

$$\begin{array}{c}

(-7) \\

+ (+2) \\

\hline

(-5)

\end{array}

+ \begin{array}{c}

0 \ 0 \ 0 \ 0 \ 0 \\

+ 0 \ 0 \ 1 \ 0 \\

\hline

1 \ 0 \ 1 \ 1

\end{array}$$

$$\begin{pmatrix} c_4 = 1 \\ c_3 = 0 \end{pmatrix}$$

$c_4 = 0$ <br/> $c_3 = 0$

Overflow occurs only in these two cases.

$$\begin{aligned}

c_4 &= 0 \\

c_3 &= 1

\end{aligned}$$

$$\begin{array}{c}

(+7) \\

+(+2) \\

(+9)

\end{array}

+

\begin{array}{c}

0 \ 1 \ 1 \ 0 \ 0 \\

0 \ 1 \ 1 \ 1 \\

0 \ 0 \ 1 \ 0 \\

1 \ 0 \ 0 \ 1

\end{array}$$

$$\begin{array}{c}

(-7) \\

+ (+2) \\

\hline

(-5)

\end{array}

+

\begin{array}{c}

0 \ 0 \ 0 \ 0 \ 0 \\

+ 0 \ 0 \ 1 \ 0 \\

\hline

1 \ 0 \ 1 \ 1

\end{array}$$

$$c_4 = 0$$

$$c_3 = 0$$

$$c_4 = 1$$

$c_3 = 1$

$(+7)$

$+ (-2)$

(+5)

$$+ \frac{11100}{1110} \\

+ \frac{1110}{10101}$$

$$\begin{array}{c}

(-7) \\

+ (-2) \\

\hline

(-9)

\end{array}

+ \begin{array}{c}

10000 \\

1001 \\

1110

\end{array}$$

$$\begin{pmatrix}

c_4 = 1 \\

c_3 = 0

\end{pmatrix}$$

Overflow =

$$c_3\overline{c}_4 + \overline{c}_3c_4$$

$$\begin{pmatrix}

c_4 = 0 \\

c_3 = 1

\end{pmatrix}$$

$$\begin{array}{c}

(+7) \\

+(+2) \\

\hline

(+9)

\end{array}

+

\begin{array}{c}

0 \ 1 \ 1 \ 0 \ 0 \\

0 \ 1 \ 1 \ 1 \\

0 \ 0 \ 1 \ 0 \\

\hline

1 \ 0 \ 0 \ 1

\end{array}$$

$$c_4 = 0$$

$$c_3 = 0$$

$$c_4 = 1$$

$c_3 = 1$

$(+7)$

$+ (-2)$

$(+5)$

$$+ \frac{\begin{array}{r} 1 & 1 & 1 & 0 & 0 \\ & 0 & 1 & 1 & 1 \\ & & 1 & 1 & 1 & 0 \\ \hline & 1 & 0 & 1 & 0 & 1 \end{array}$$

$$\begin{pmatrix} c_4 = 1 \\ c_3 = 0 \end{pmatrix}$$

Overflow =

$$c_3\overline{c}_4 + \overline{c}_3c_4$$

XOR

# Calculating overflow for 4-bit numbers with only three significant bits

Overflow =

$$c_3\bar{c}_4 + \bar{c}_3c_4$$

=  $c_3 \oplus c_4$

# Calculating overflow for n-bit numbers with only n-1 significant bits

Overflow =

$$c_{n-1} \oplus c_n$$

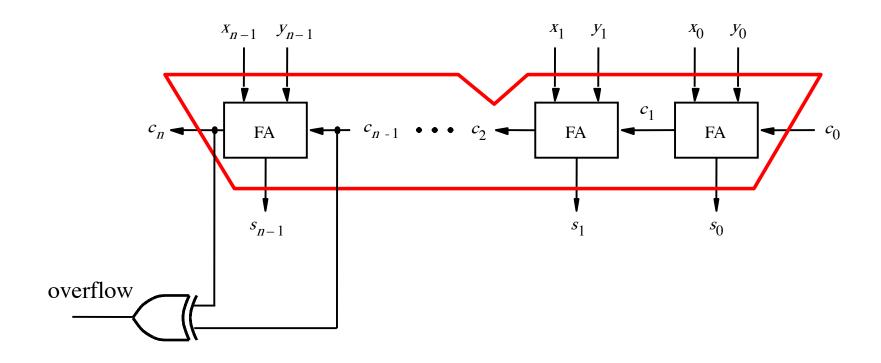

## **Detecting Overflow**

# Detecting Overflow (with one extra XOR)

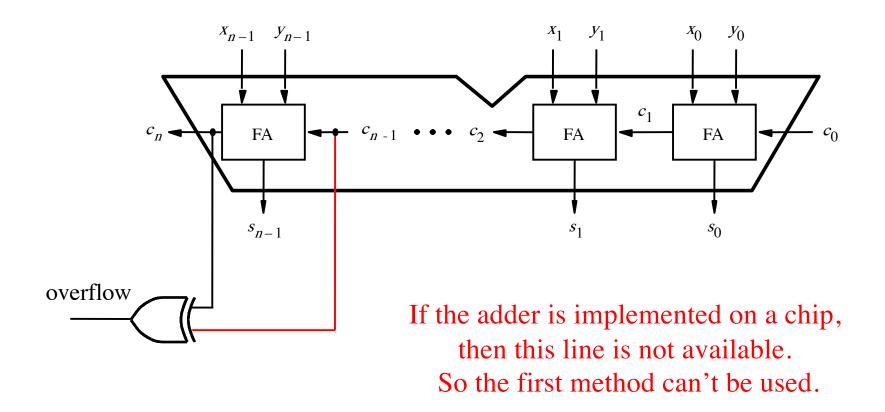

## Detecting Overflow (alternative method)

Used if you don't have access to the internal carries of the adder.

# Detecting Overflow (with one extra XOR)

#### **Overflow Detection: 4-bits**

#### **Overflow Detection: 5-bits**

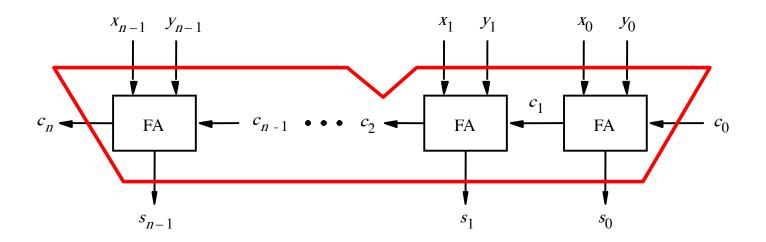

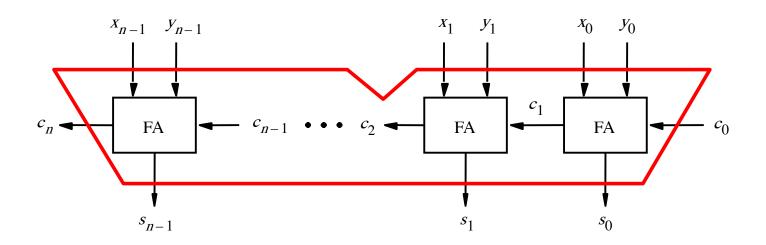

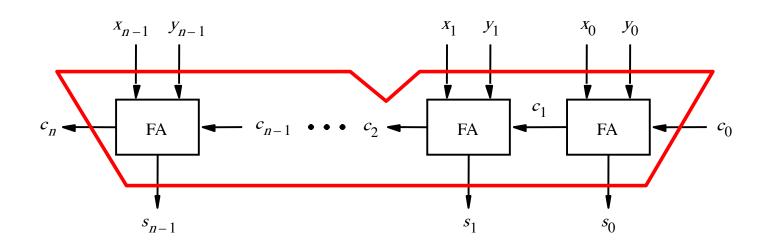

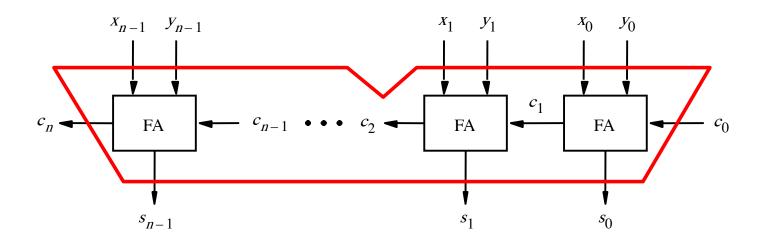

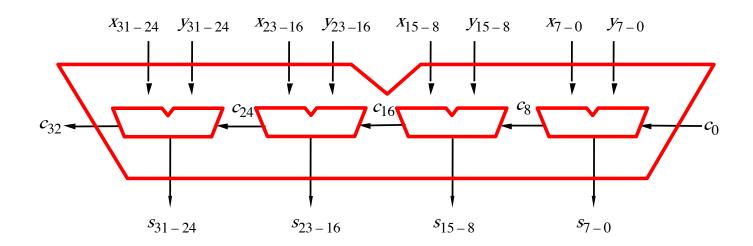

A ripple-carry adder

# How long does it take to compute all sum bits and all carry bits?

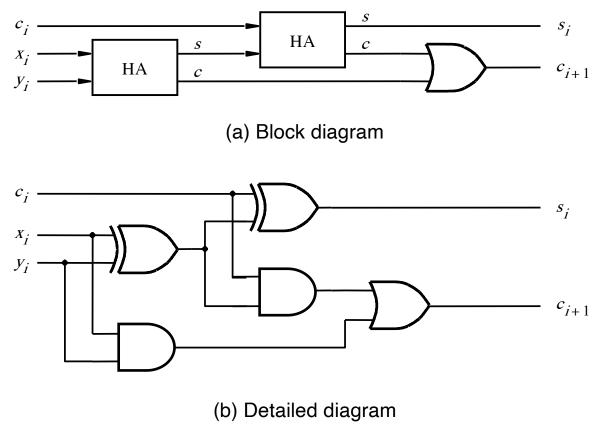

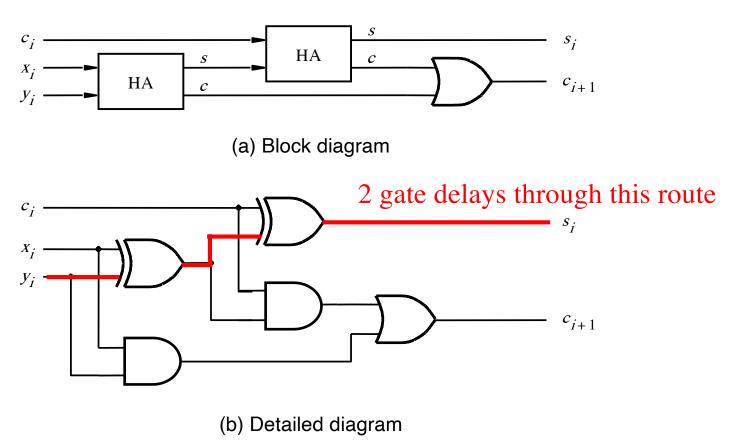

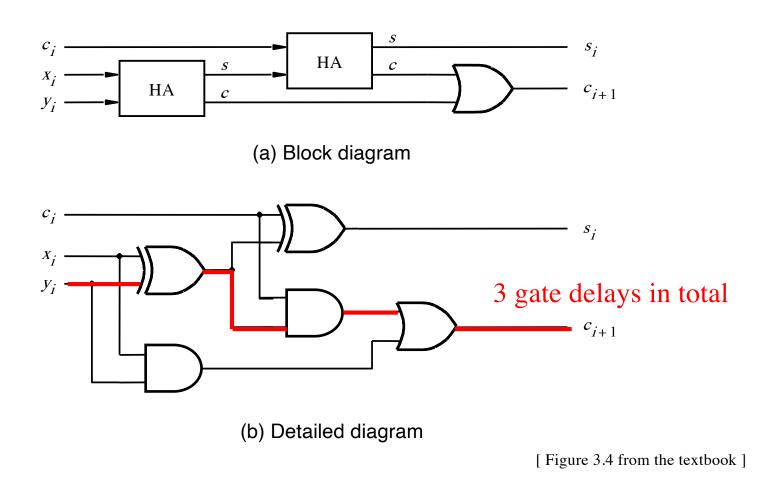

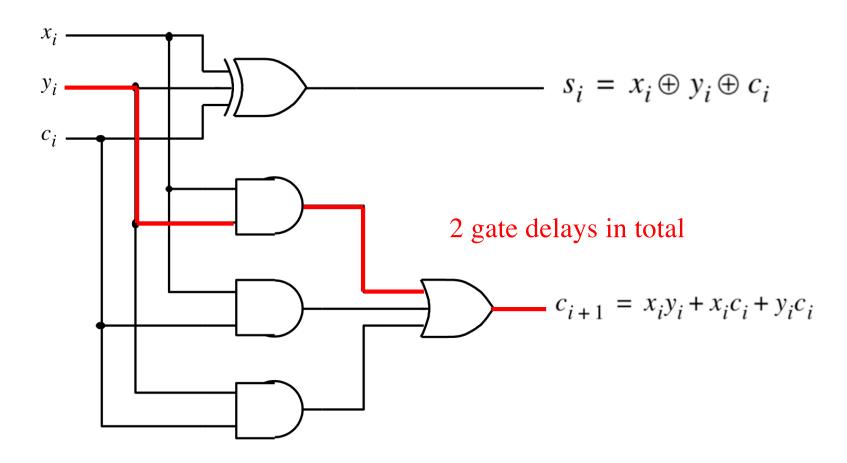

# Delays through the modular implementation of the full-adder circuit

[ Figure 3.4 from the textbook ]

# Delays through the modular implementation of the full-adder circuit

[ Figure 3.4 from the textbook ]

# Delays through the modular implementation of the full-adder circuit

# How long does it take to compute all sum bits and all carry bits in this case?

It takes 3n gate delays?

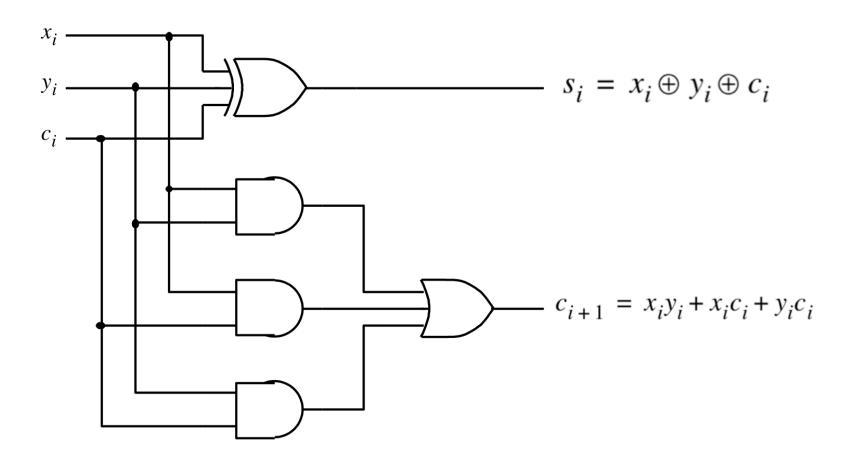

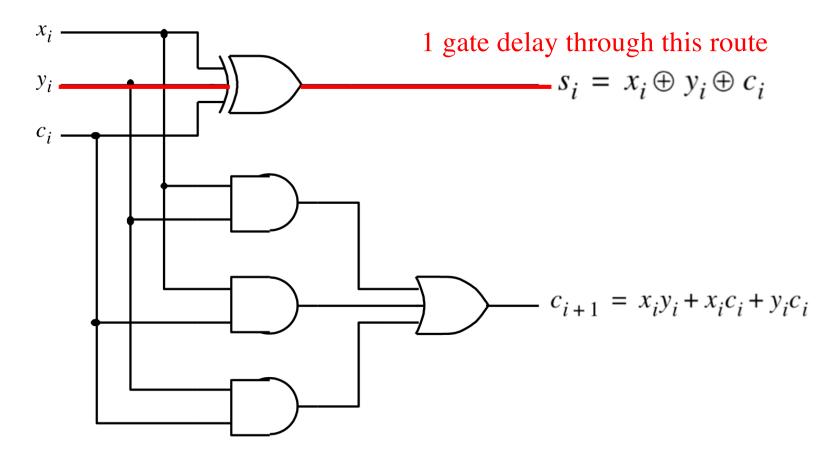

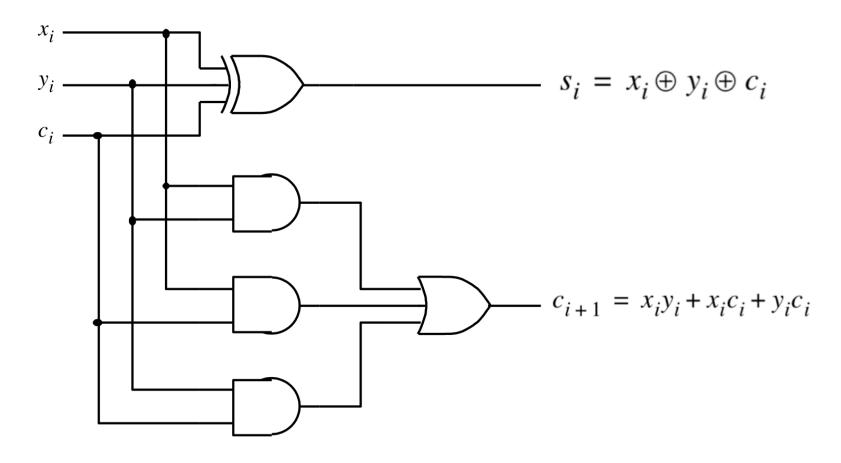

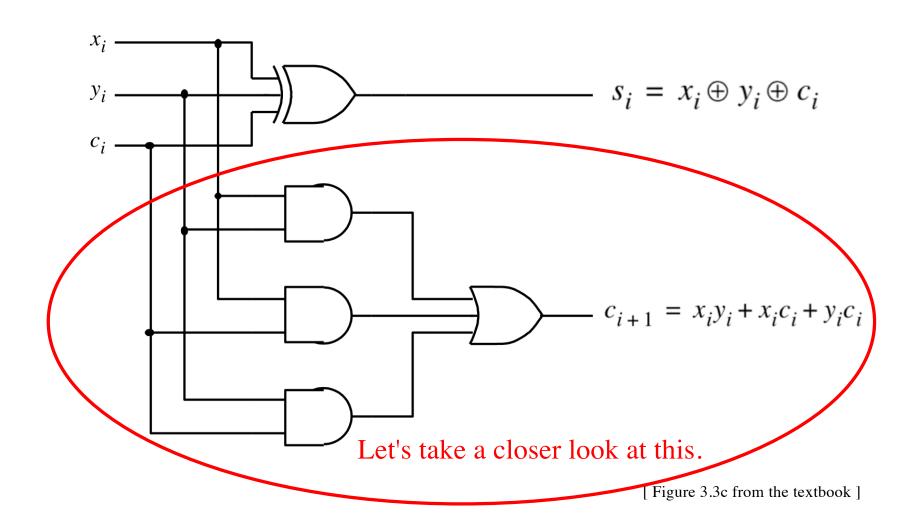

## Delays through the Full-Adder circuit

[ Figure 3.3c from the textbook ]

### Delays through the Full-Adder circuit

[ Figure 3.3c from the textbook ]

## Delays through the Full-Adder circuit

[ Figure 3.3c from the textbook ]

# How long does it take to compute all sum bits and all carry bits?

It takes 2n gate delays?

#### Can we perform addition even faster?

The goal is to evaluate very fast if the carry from the previous stage will be equal to 0 or 1.

#### Can we perform addition even faster?

The goal is to evaluate very fast if the carry from the previous stage will be equal to 0 or 1.

To accomplish this goal we will have to redesign the full-adder circuit yet again.

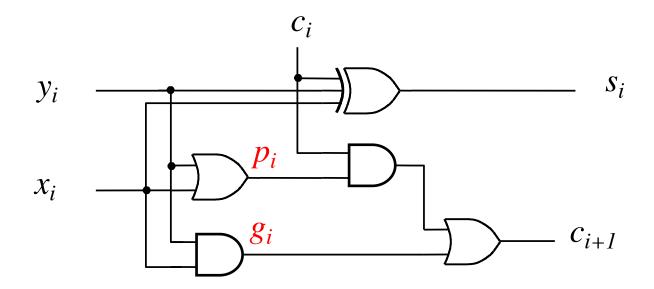

#### The Full-Adder Circuit

[ Figure 3.3c from the textbook ]

#### The Full-Adder Circuit

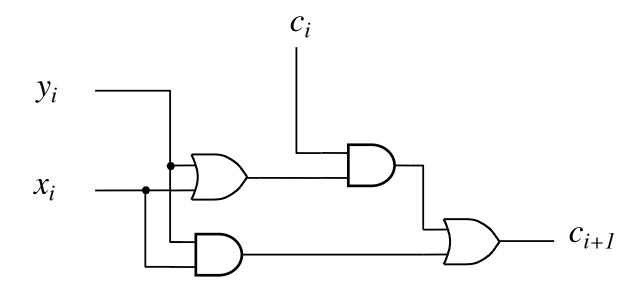

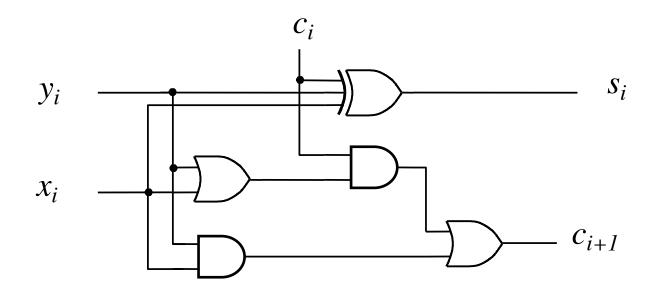

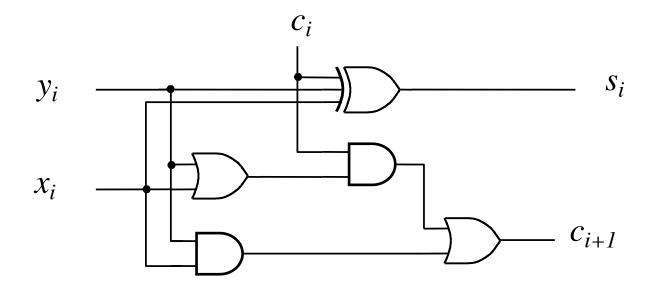

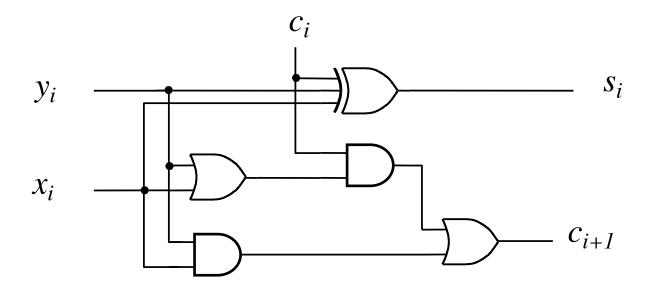

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i)c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i)c_i$$

$$c_{i+1} = \underbrace{x_i y_i}_{g_i} + (\underbrace{x_i + y_i}_{p_i})c_i$$

g - generate

p - propagate

$$c_{i+1} = \underbrace{x_i y_i}_{g_i} + (\underbrace{x_i + y_i}_{p_i})c_i$$

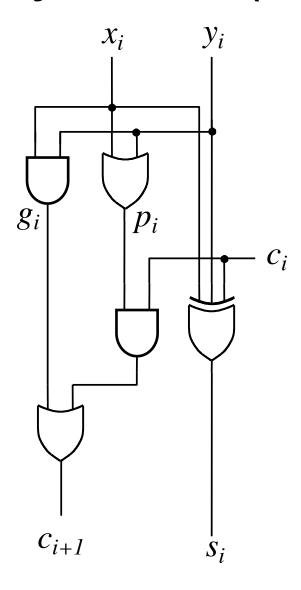

## Yet Another Way to Draw It (Just Rotate It)

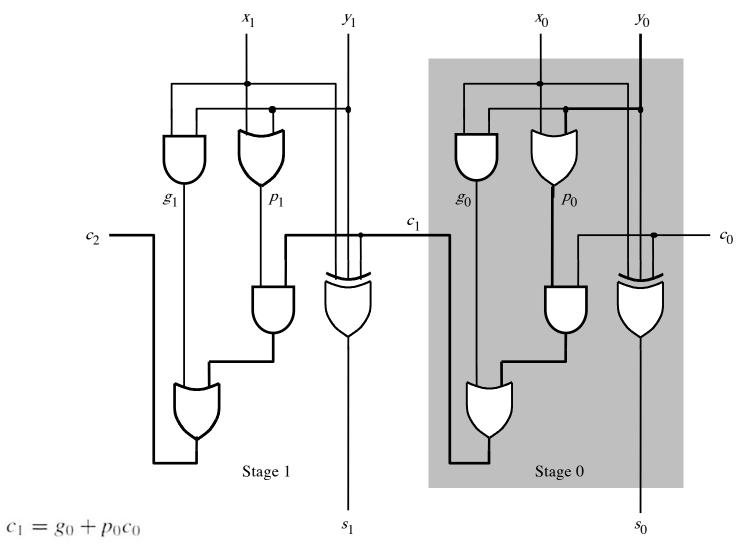

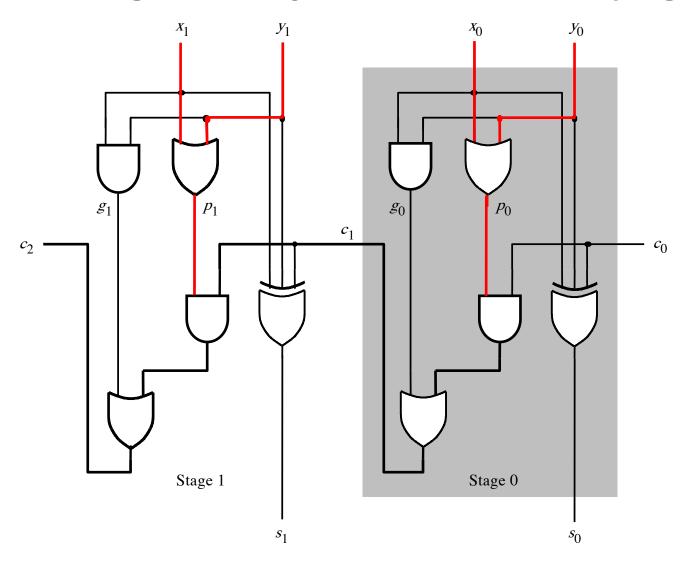

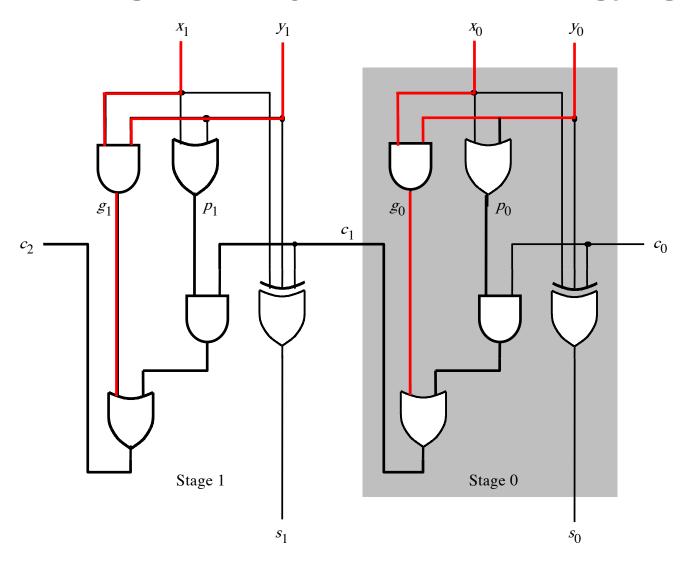

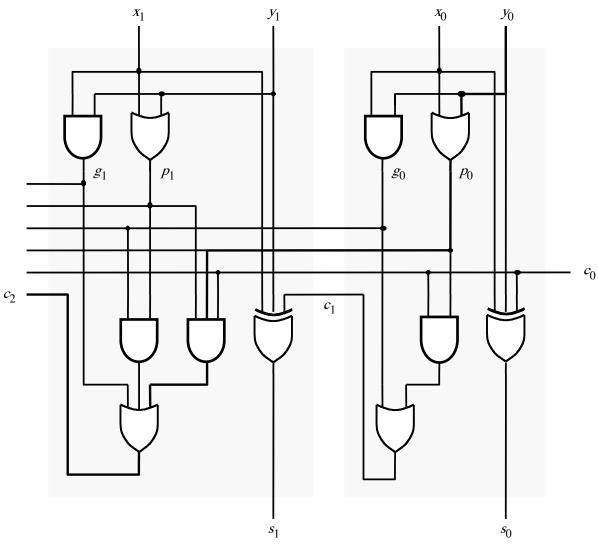

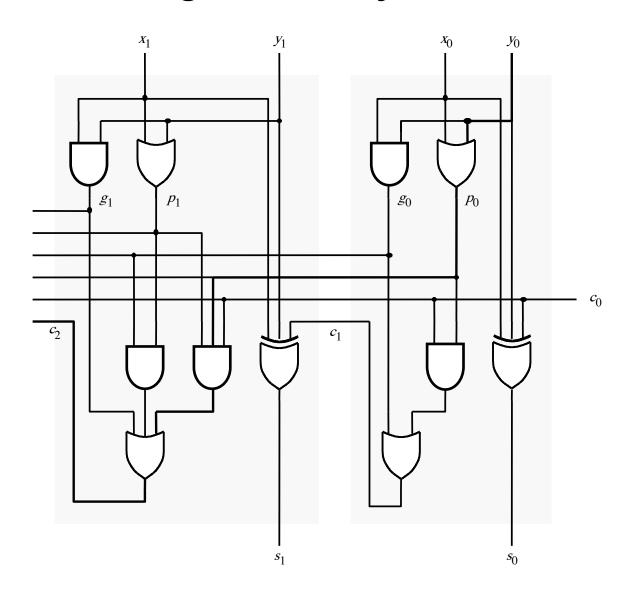

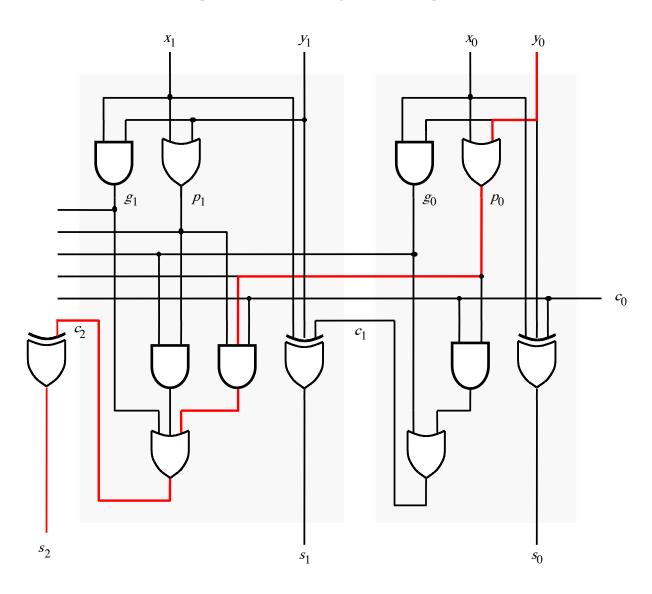

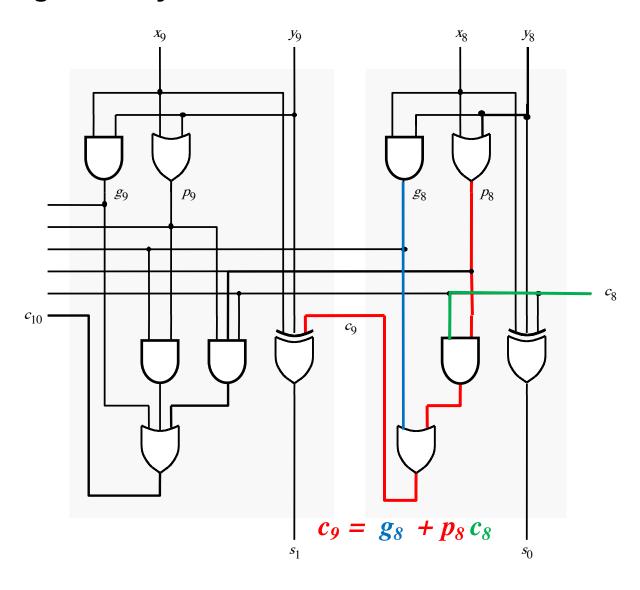

#### Now we can Build a Ripple-Carry Adder

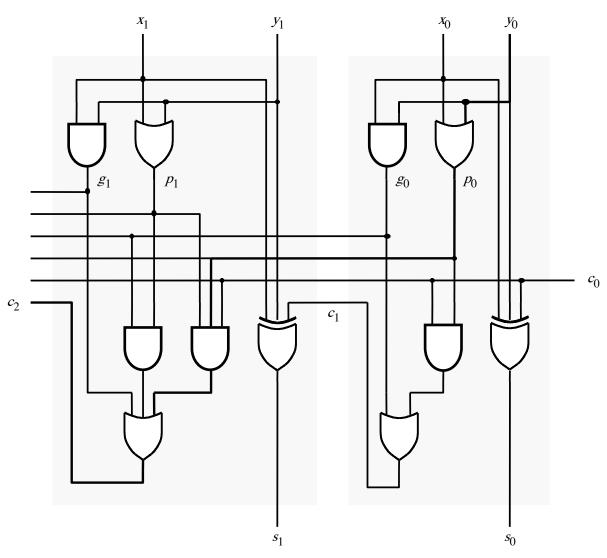

$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$

[ Figure 3.14 from the textbook ]

#### Now we can Build a Ripple-Carry Adder

$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$

[ Figure 3.14 from the textbook ]

## 2-bit ripple-carry adder: 5 gate delays (1+2+2)

## n-bit ripple-carry adder: 2n+1 gate delays

#### n-bit Ripple-Carry Adder

- It takes 1 gate delay to generate all g<sub>i</sub> and p<sub>i</sub> signals

- +2 more gate delays to generate carry 1

- +2 more gate delay to generate carry 2

---

- +2 more gate delay to generate carry n

- Thus, the total delay through an n-bit ripple-carry adder is 2n+1 gate delays!

#### n-bit Ripple-Carry Adder

- It takes 1 gate delay to generate all g<sub>i</sub> and p<sub>i</sub> signals

- +2 more gate delays to generate carry 1

- +2 more gate delay to generate carry 2

...

- +2 more gate delay to generate carry n

- Thus, the total delay through an n-bit ripple-carry adder is 2n+1 gate delays!

This is slower by 1 than the original design?!

# A carry-lookahead adder

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$g_i \qquad p_i$$

(1 gate delay) (1 gate delay)

#### It takes 1 gate delay to compute all p<sub>i</sub> signals

[ Figure 3.14 from the textbook ]

## It takes 1 gate delay to compute all gi signals

[ Figure 3.14 from the textbook ]

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = g_i + p_i c_i$$

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = g_i + p_i c_i$$

$$c_{i+1} = g_i + p_i (g_{i-1} + p_{i-1} c_{i-1})$$

$$c_{i+1} = g_i + p_i (g_{i-1} + p_{i-1} c_{i-1})$$

recursive expansion of

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = g_i + p_i c_i$$

$$c_{i+1} = g_i + p_i (g_{i-1} + p_{i-1} c_{i-1})$$

$$c_{i+1} = g_i + p_i g_{i-1} + p_i p_{i-1} c_{i-1}$$

## Now we can Build a Carry-Lookahead Adder

[ Figure 3.15 from the textbook ]

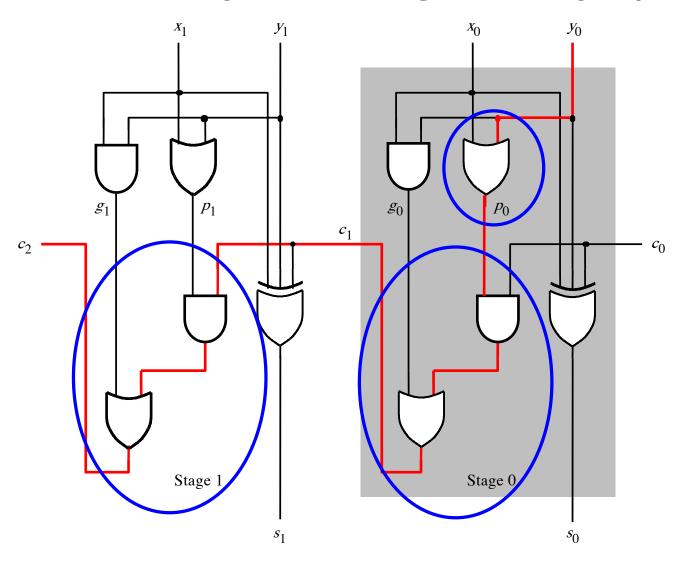

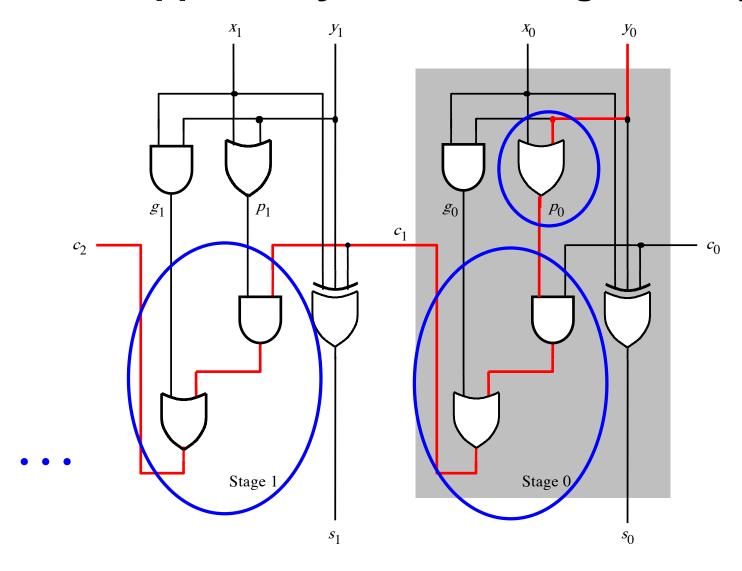

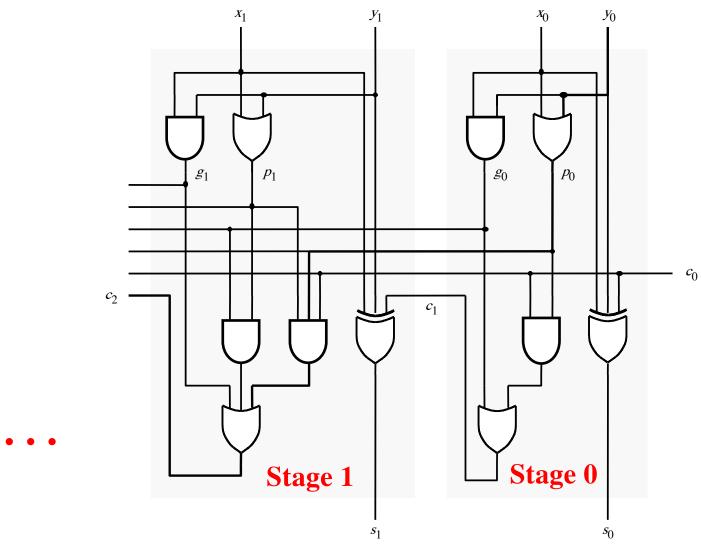

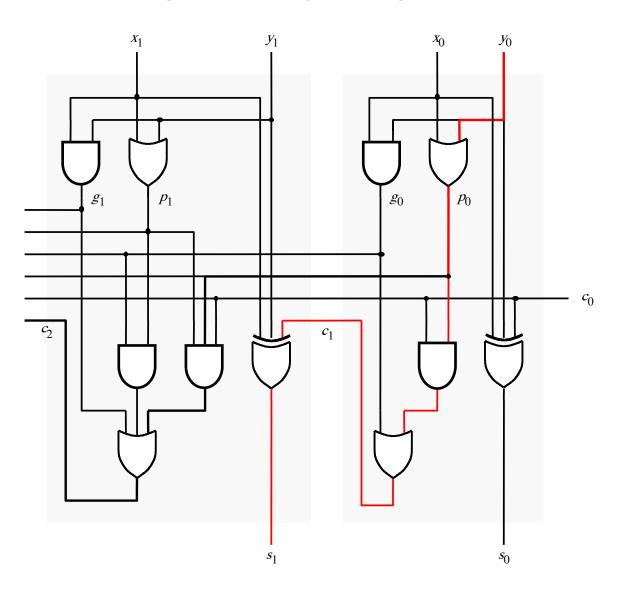

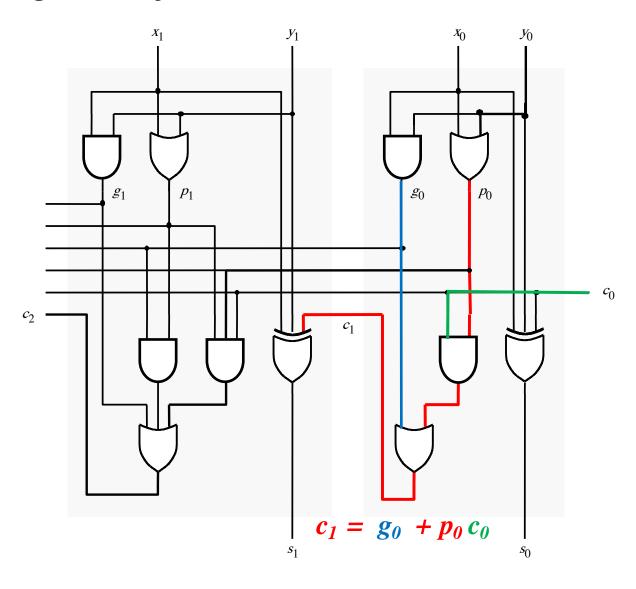

#### The first two stages of a carry-lookahead adder

[ Figure 3.15 from the textbook ]

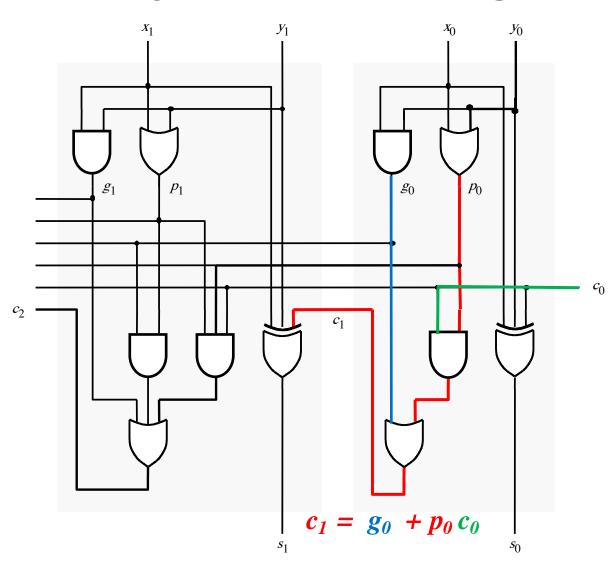

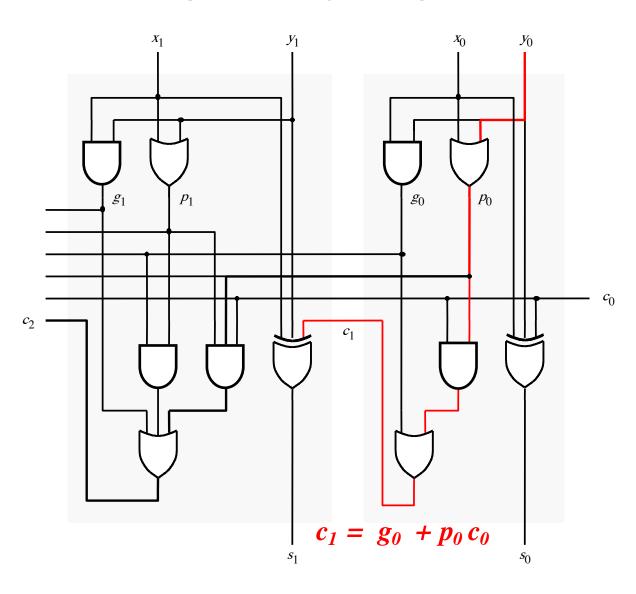

## Carry for the first stage

$$c_1 = g_0 + p_0 c_0$$

## **Carry for the first stage**

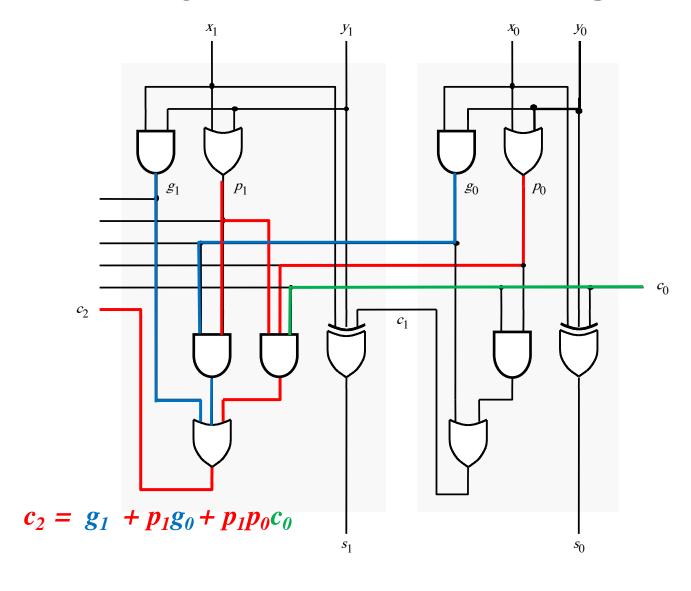

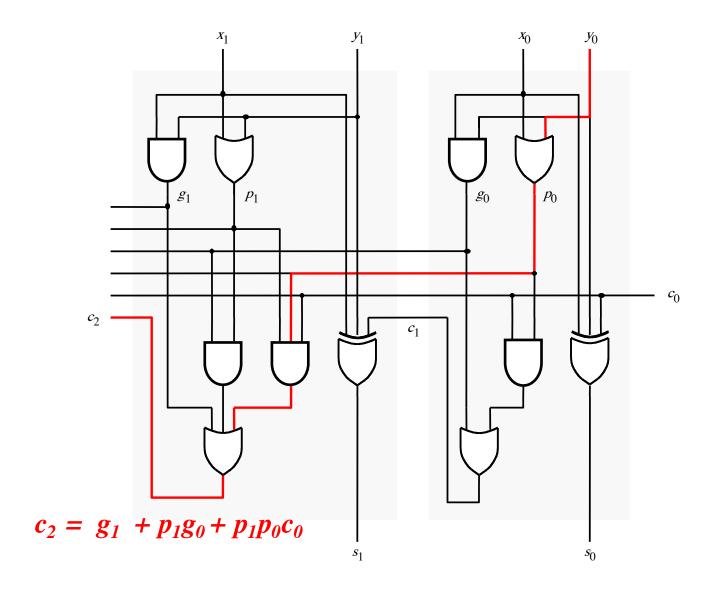

# Carry for the second stage

$$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$$

## Carry for the second stage

$$c_1 = g_0 + p_0 c_0$$

$$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$$

$$c_1 = g_0 + p_0 c_0$$

$$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$$

$$c_{1} = g_{0} + p_{0}c_{0}$$

$$c_{2} = g_{1} + p_{1}g_{0} + p_{1}p_{0}c_{0}$$

$$= g_{1} + p_{1}(g_{0} + p_{0}c_{0})$$

$$c_{1} = g_{0} + p_{0}c_{0}$$

$$c_{2} = g_{1} + p_{1}g_{0} + p_{1}p_{0}c_{0}$$

$$= g_{1} + p_{1}(g_{0} + p_{0}c_{0})$$

$$= g_{1} + p_{1}c_{1}$$

#### The first two stages of a carry-lookahead adder

[ Figure 3.15 from the textbook ]

#### It takes 3 gate delays to generate c<sub>1</sub>

#### It takes 3 gate delays to generate c<sub>2</sub>

#### The first two stages of a carry-lookahead adder

#### It takes 4 gate delays to generate s<sub>1</sub>

#### It takes 4 gate delays to generate s<sub>2</sub>

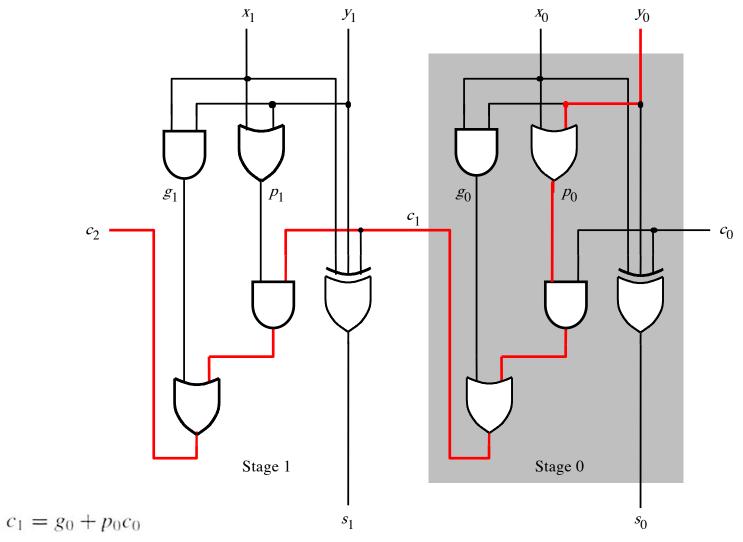

#### N-bit Carry-Lookahead Adder

- It takes 1 gate delay to generate all g<sub>i</sub> and p<sub>i</sub> signals

- It takes 2 more gate delays to generate all carry signals

- It takes 1 more gate delay to generate all sum bits

Thus, the total delay through an n-bit carry-lookahead adder is only 4 gate delays!

#### N-bit Carry-Lookahead Adder

- It takes 1 gate delay to generate all g<sub>i</sub> and p<sub>i</sub> signals

- It takes 2 more gate delays to generate all carry signals

- It takes 1 more gate delay to generate all sum bits

Thus, the total delay through an n-bit carry-lookahead adder is only 4 gate delays!

#### **Expanding the Carry Expression**

$$c_{i+1} = g_i + p_i c_i$$

$$c_1 = g_0 + p_0 c_0$$

$$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$$

$$c_3 = g_2 + p_2 g_1 + p_2 p_1 g_0 + p_2 p_1 p_0 c_0$$

$$\cdots$$

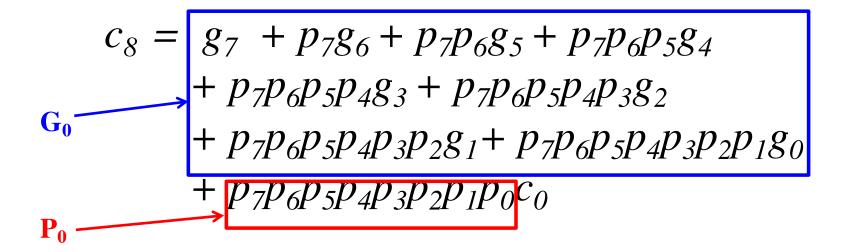

$$c_8 = g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4$$

$$+ p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2$$

$$+ p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0$$

$$+ p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0$$

### **Expanding the Carry Expression**

$$c_{i+1} = g_i + p_i c_i$$

$$c_1 = g_0 + p_0 c_0$$

$$c_2 = g_1 + p_1 g_0 + p_1 p_0 c_0$$

$$c_3 = g_2 + p_2 g_1 + p_2 p_1 g_0 + p_2 p_1 p_0 c_0$$

$$\cdots$$

$$c_8 = g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4$$

Even this takes  $+ p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2$

only 3 gate delays  $+ p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0$

$$+ p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0$$

[ Figure 3.17 from the textbook ]

$$c_8 = g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4$$

$$+ p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2$$

$$+ p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0$$

$$+ p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0$$

$$c_8 = g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4 + p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2 + p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0$$

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$c_8 = G_0 + P_0 c_0$$

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$2-\text{gate delays}$$

$$c_8 = G_0 + P_0 c_0$$

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$2-\text{gate delays}$$

$$c_8 = G_0 + P_0 c_0$$

3-gate 2-gate delays

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$2-\text{gate delays}$$

$$c_8 = G_0 + P_0 c_0$$

3-gate

delays

delays

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$2-\text{gate delays}$$

$$c_8 = G_0 + P_0 c_0$$

4-gate delays

$$c_8 = g_7 + p_7g_6 + p_7p_6g_5 + p_7p_6p_5g_4$$

$$+ p_7p_6p_5p_4g_3 + p_7p_6p_5p_4p_3g_2$$

$$+ p_7p_6p_5p_4p_3p_2g_1 + p_7p_6p_5p_4p_3p_2p_1g_0$$

$$+ p_7p_6p_5p_4p_3p_2p_1p_0c_0$$

$$c_{16} = g_{15} + p_{15}g_{14} + p_{15}p_{14}g_{13} + p_{15}p_{14}p_{13}g_{12} + p_{15}p_{14}p_{13}p_{12}g_{11} + p_{15}p_{14}p_{13}p_{12}p_{11}g_{10} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}g_{9} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}g_{8} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}p_{8}c_{8}$$

$$c_8 = g_7 + p_7g_6 + p_7p_6g_5 + p_7p_6p_5g_4$$

$$+ p_7p_6p_5p_4g_3 + p_7p_6p_5p_4p_3g_2$$

$$+ p_7p_6p_5p_4p_3p_2g_1 + p_7p_6p_5p_4p_3p_2p_1g_0$$

$$+ p_7p_6p_5p_4p_3p_2p_1p_0c_0$$

The same expression, just add 8 to all subscripts

$$c_{16} = g_{15} + p_{15}g_{14} + p_{15}p_{14}g_{13} + p_{15}p_{14}p_{13}g_{12} + p_{15}p_{14}p_{13}p_{12}g_{11} + p_{15}p_{14}p_{13}p_{12}p_{11}g_{10} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}g_{9} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}g_{8} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}p_{8}c_{8}$$

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4}$$

$$+ p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

$$2-\text{gate delays}$$

$$c_{16} = g_{15} + p_{15}g_{14} + p_{15}p_{14}g_{13} + p_{15}p_{14}p_{13}g_{12} + p_{15}p_{14}p_{13}p_{12}g_{11} + p_{15}p_{14}p_{13}p_{12}p_{11}g_{10} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}g_{9} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}g_{8} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}p_{8}c_{8}$$

$$c_8 = g_7 + p_7g_6 + p_7p_6g_5 + p_7p_6p_5g_4$$

$$+ p_7p_6p_5p_4g_3 + p_7p_6p_5p_4p_3g_2$$

$$+ p_7p_6p_5p_4p_3p_2g_1 + p_7p_6p_5p_4p_3p_2p_1g_0$$

$$+ p_7p_6p_5p_4p_3p_2p_1p_0c_0$$

$$c_{16} = g_{15} + p_{15}g_{14} + p_{15}p_{14}g_{13} + p_{15}p_{14}p_{13}g_{12} + p_{15}p_{14}p_{13}p_{12}g_{11} + p_{15}p_{14}p_{13}p_{12}p_{11}g_{10} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}g_{9} + p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}g_{8}$$

$$+ p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}p_{8}c_{8}$$

$$+ p_{15}p_{14}p_{13}p_{12}p_{11}p_{10}p_{9}p_{8}c_{8}$$

$$-2-gate delays$$

$$c_8 = G_0 + P_0 c_0$$

$$c_8 = G_0 + P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

2-gate delays

$$c_8 = G_0 + P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

4-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

=  $G_1 + P_1 G_0 + P_1 P_0 c_0$

$$c_8 = G_0 + P_0 c_0$$

3-gate delays

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

3-gate delays

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

2-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

4-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

2-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

2-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

3-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

$$= G_1 + P_1 G_0 + P_1 P_0 c_0$$

5-gate delays

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8$$

=  $G_1 + P_1 G_0 + P_1 P_0 c_0$

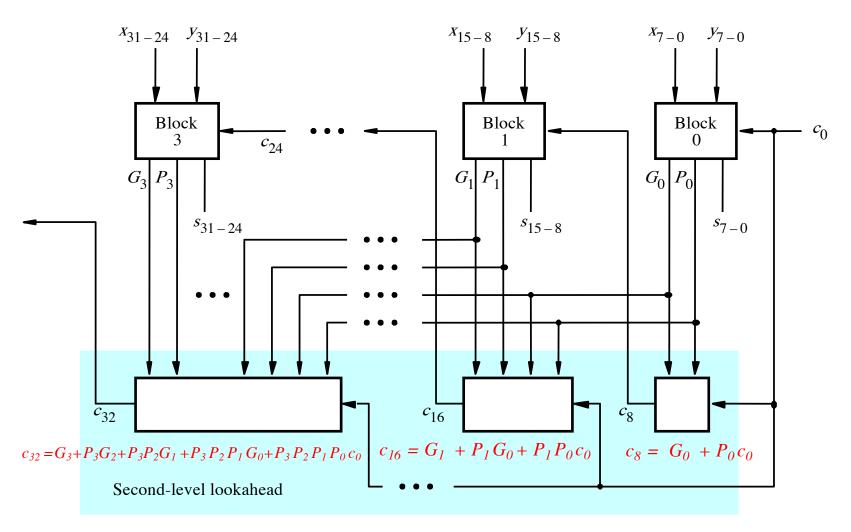

$$c_{24} = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 c_0$$

$$c_{32} = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_0$$

$$c_8 = G_0 + P_0 c_0$$

4-gate delays

$$c_{16} = G_1 + P_1 c_8$$

5-gate delays

=  $G_1 + P_1 G_0 + P_1 P_0 c_0$

$c_{24} = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0c_0$  5-gate delays

5-gate delays

$$c_{32} = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_0$$

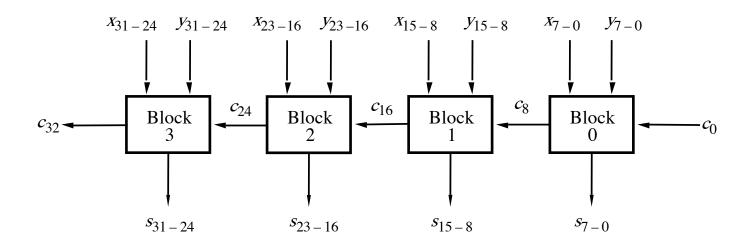

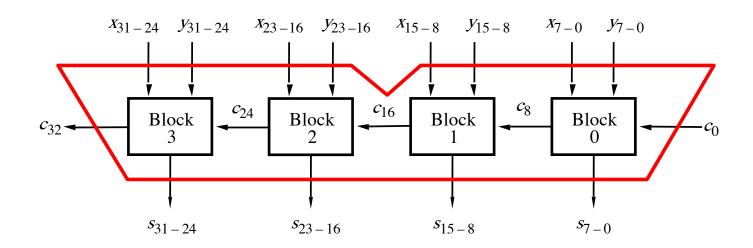

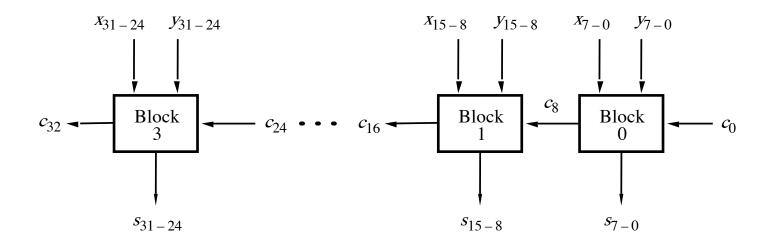

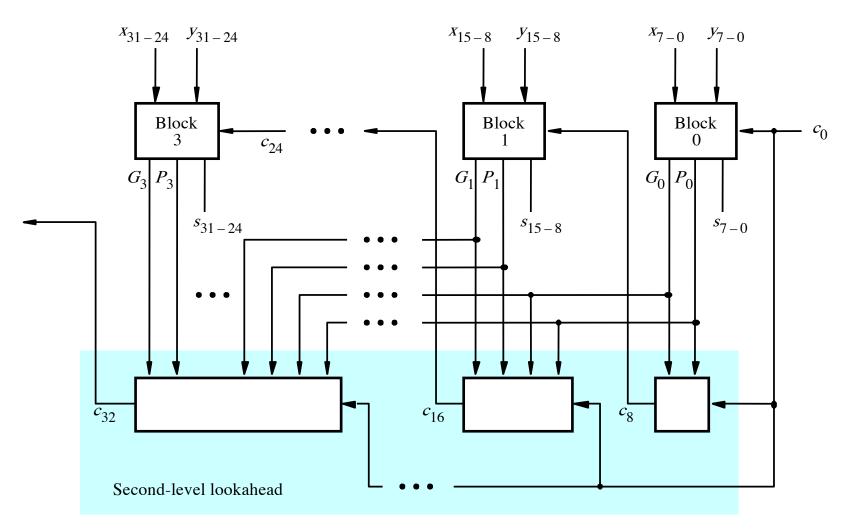

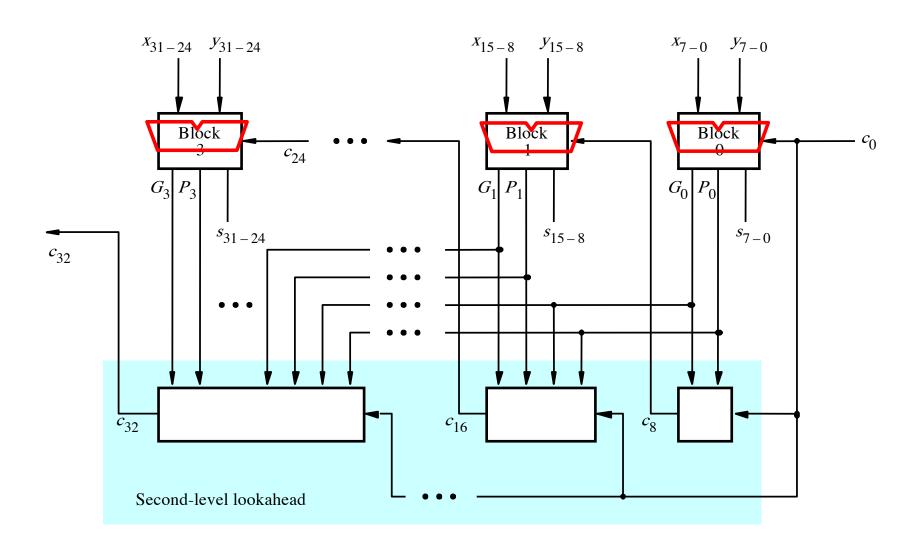

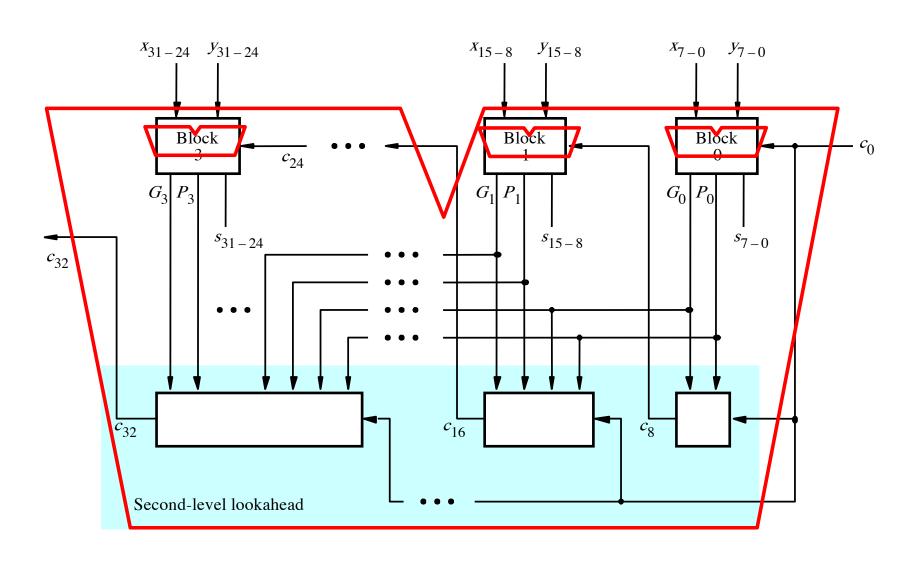

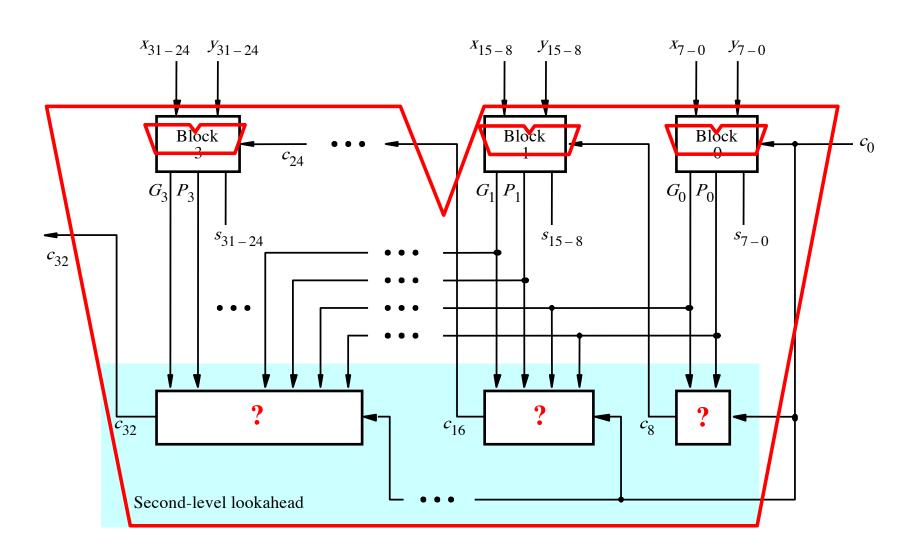

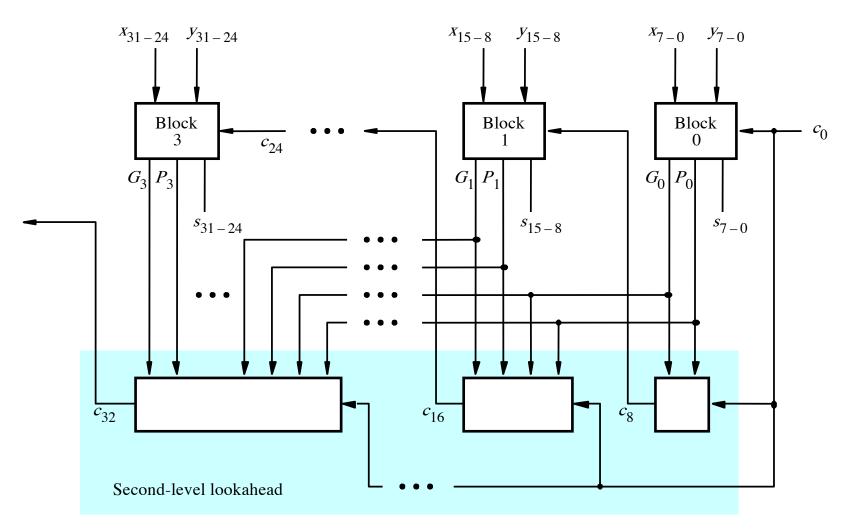

#### A hierarchical carry-lookahead adder

[ Figure 3.17 from the textbook ]

#### A hierarchical carry-lookahead adder

[ Figure 3.17 from the textbook ]

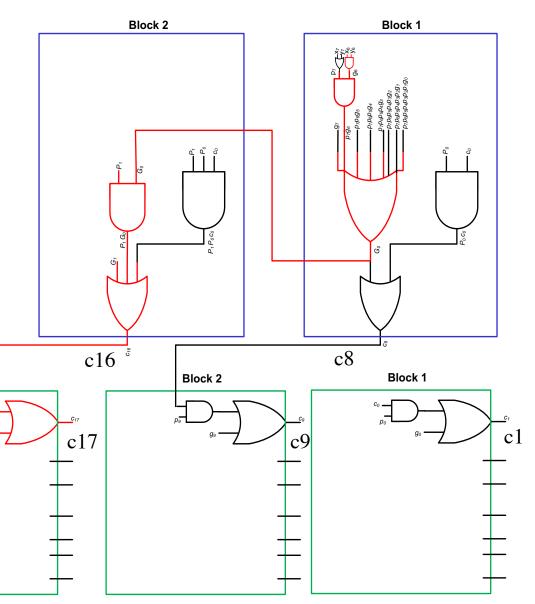

# Total Gate Delay Through a Hierarchical Carry-Lookahead Adder

- The total delay is 8 gates:

- 3 to generate all Gi and Pi signals

- +2 to generate c8, c16, c24, and c32

- +2 to generate internal carries in the blocks

- +1 to generate the sum bits (one extra XOR)

# Total Gate Delay Through a Hierarchical Carry-Lookahead Adder

- The total delay is 8 gates:

- 3 to generate all Gi and Pi signals

- +2 to generate c8, c16, c24, and c32

- +2 to generate internal carries in the blocks

- +1 to generate the sum bits (one extra XOR)

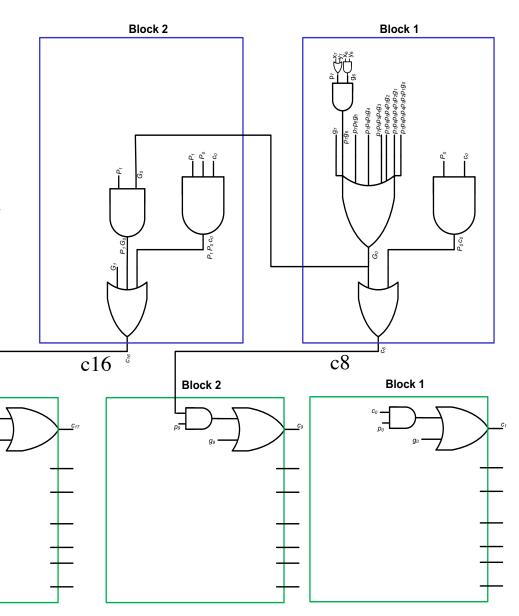

#### 2 more gate delays for the internal carries within a block

#### 2 more gate delays for the internal carries within a block

# Hierarchical Carry-Lookahead Adder (Carry Logic)

SECOND LEVEL HIERARCHY

Block 3

C8 - 4 gate delays

C16 – 5 gate delays

C24 – 5 Gate delays

C32 – 5 Gate delays

FIRST LEVEL HIERARCHY

# Hierarchical Carry-Lookahead Adder (Critical Path)

SECOND LEVEL HIERARCHY

Block 3

C1 - 3 gate delays

C9 - 6 gate delays

C17 – 7 gate delays

C25 – 7 Gate delays

FIRST LEVEL HIERARCHY

# Total Gate Delay Through a Hierarchical Carry-Lookahead Adder

- The total delay is 8 gates:

- 3 to generate all Gi and Pi signals

- +2 to generate c8, c16, c24, and c32

- +2 to generate internal carries in the blocks

- +1 to generate the sum bits (one extra XOR)

**Questions?**

## THE END